- 您现在的位置:买卖IC网 > PDF目录205935 > XC5204-6TQ144C (XILINX INC) Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | XC5204-6TQ144C |

| 厂商: | XILINX INC |

| 元件分类: | FPGA |

| 英文描述: | Field Programmable Gate Arrays |

| 中文描述: | FPGA, 120 CLBS, 4000 GATES, 83 MHz, PQFP144 |

| 封装: | PLASTIC, TQFP-144 |

| 文件页数: | 4/73页 |

| 文件大小: | 598K |

| 代理商: | XC5204-6TQ144C |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

R

XC5200 Series Field Programmable Gate Arrays

7-94

November 5, 1998 (Version 5.2)

CLB inputs have several possible sources: the 24 signals

from the GRM, 16 direct connections from neighboring

VersaBlocks, four signals from global, low-skew buffers,

and the four signals from the CLB output multiplexers.

Unlike the output multiplexers, the input multiplexers are

not fully populated; i.e., only a subset of the available sig-

nals can be connected to a given CLB input. The flexibility

of LUT input swapping and LUT mapping compensates for

this limitation. For example, if a 2-input NAND gate is

required, it can be mapped into any of the four LUTs, and

use any two of the four inputs to the LUT.

Direct Connects

The unidirectional direct-connect segments are connected

to the logic input/output pins through the CLB input and out-

put multiplexer arrays, and thus bypass the general routing

matrix altogether. These lines increase the routing channel

utilization,

while

simultaneously

reducing

the

delay

incurred in speed-critical connections.

The direct connects also provide a high-speed path from

the edge CLBs to the VersaRing input/output buffers, and

thus reduce pin-to-pin set-up time, clock-to-out, and combi-

national propagation delay. Direct connects from the input

buffers to the CLB DI pin (direct flip-flop input) are only

available on the left and right edges of the device. CLB

look-up table inputs and combinatorial/registered outputs

have direct connects to input/output buffers on all four

sides.

The direct connects are ideal for developing customized

RPM cells. Using direct connects improves the macro per-

formance, and leaves the other routing channels intact for

improved routing. Direct connects can also route through a

CLB using one of the four cell-feedthrough paths.

General Routing Matrix

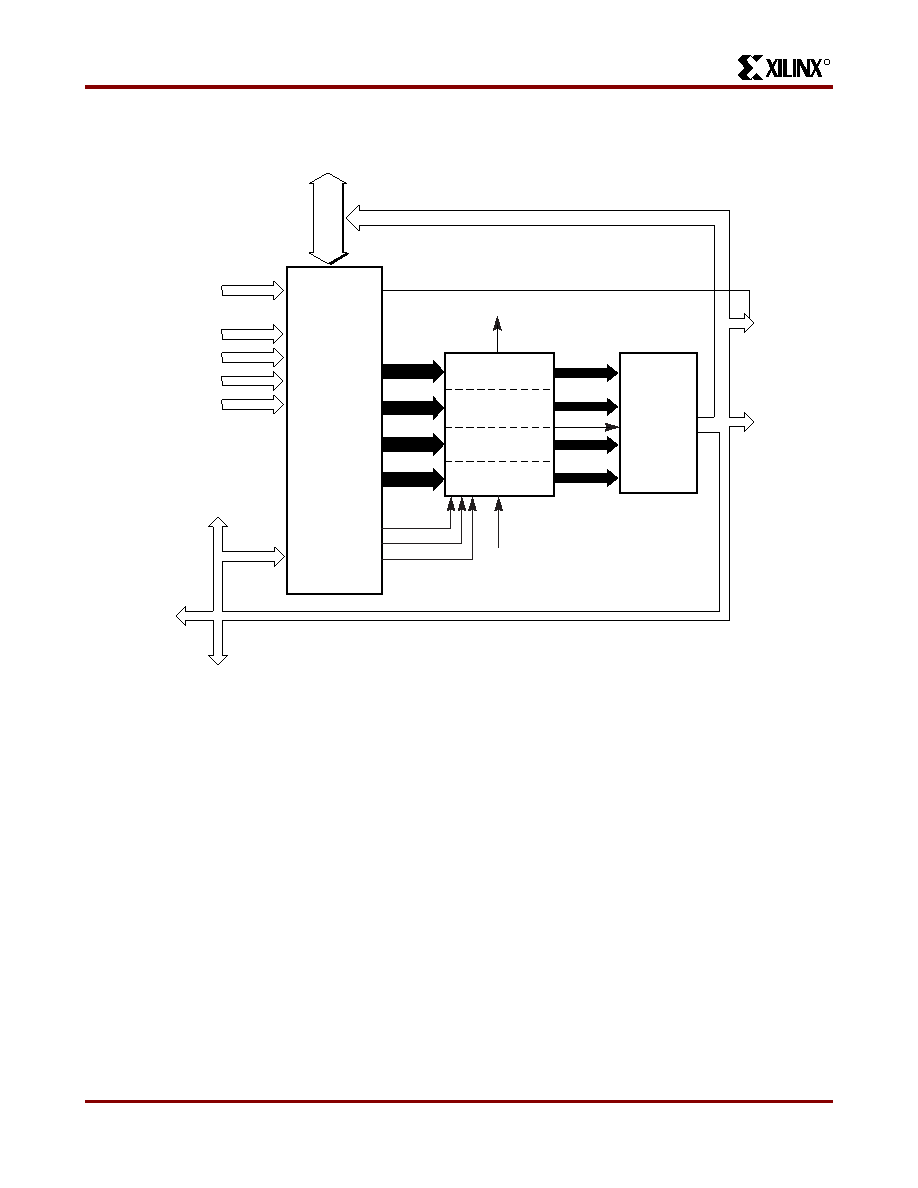

The General Routing Matrix, shown in Figure 15, provides

flexible bidirectional connections to the Local Interconnect

Figure 14: VersaBlock Details

4

5

3

24

To GRM

M0-M23

CLB

CLK

Direct North

Direct to

East

To

Longlines

and GRM

TQ0-TQ3

Global Nets

Feedback

Direct West

Direct South

CE

CLR

CIN

COUT

VCC /GND

TS

4

North

4

8

South

4

East

4

West

4

LC3

LC2

LC1

LC0

Output

Multiplexers

Input

Multiplexers

8

4

X5724

相关PDF资料 |

PDF描述 |

|---|---|

| XC5206-3BG225C | Field Programmable Gate Arrays |

| XC5206-3BG352C | Field Programmable Gate Arrays |

| XC5206-3HQ208C | Field Programmable Gate Arrays |

| XC5206-3HQ240C | Field Programmable Gate Arrays |

| XC5206-3PG156C | Field Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC5204-6TQ144I | 制造商:Xilinx 功能描述: |

| XC5204-6TQ176C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-6VQ100C | 功能描述:IC FPGA 120 CLB'S 100-VQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:XC5200 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC5204-6VQ100I | 制造商:Xilinx 功能描述: |

| XC5204-6VQ64C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。