参数资料

| 型号: | XC6SLX45T-2FG484I |

| 厂商: | Xilinx Inc |

| 文件页数: | 41/89页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN 6 484FGGBGA |

| 标准包装: | 60 |

| 系列: | Spartan® 6 LXT |

| LAB/CLB数: | 3411 |

| 逻辑元件/单元数: | 43661 |

| RAM 位总计: | 2138112 |

| 输入/输出数: | 296 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 484-BBGA |

| 供应商设备封装: | 484-FBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页

Spartan-6 FPGA Data Sheet: DC and Switching Characteristics

DS162 (v3.0) October 17, 2011

Product Specification

46

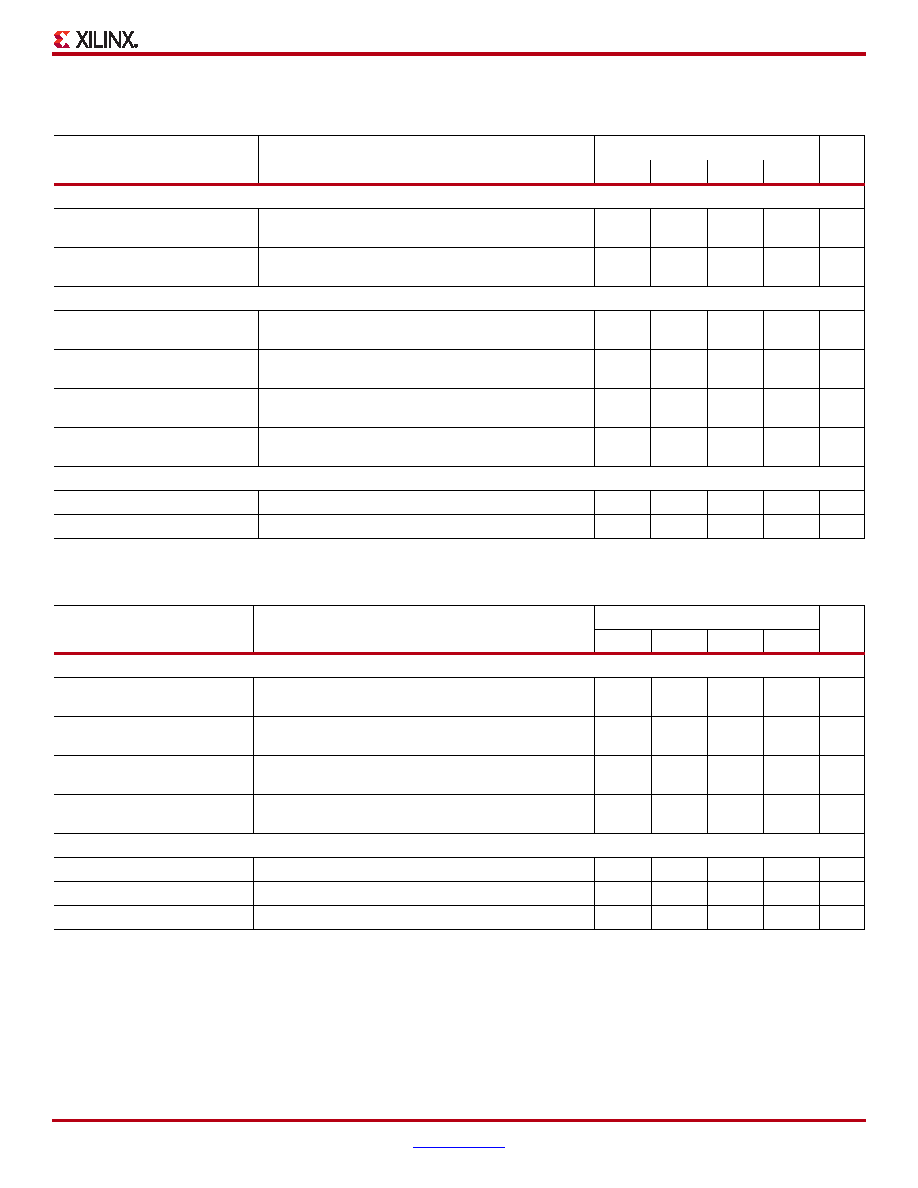

Input Serializer/Deserializer Switching Characteristics

Output Serializer/Deserializer Switching Characteristics

Table 37: ISERDES2 Switching Characteristics

Symbol

Description

Speed Grade

Units

-3

-3N

-2

-1L

Setup/Hold for Control Lines

TISCCK_BITSLIP/ TISCKC_BITSLIP

BITSLIP pin Setup/Hold with respect to CLKDIV

0.16/

–0.09

0.20/

–0.09

0.31/

–0.09

0.34/

–0.14

ns

TISCCK_CE / TISCKC_CE

CE pin Setup/Hold with respect to CLK

0.71/

–0.47

0.71/

–0.42

0.97/

–0.42

1.39/

–0.71

ns

Setup/Hold for Data Lines

TISDCK_D /TISCKD_D

D pin Setup/Hold with respect to CLK

0.24/

–0.15

0.25/

–0.05

0.29/

–0.05

0.09/

–0.05

ns

TISDCK_DDLY /TISCKD_DDLY

DDLY pin Setup/Hold with respect to CLK (using

IODELAY2)

–0.25/

0.30

–0.25/

0.42

–0.25/

0.56

–0.54/

0.67

ns

TISDCK_D_DDR /TISCKD_D_DDR

D pin Setup/Hold with respect to CLK at DDR mode

–0.03/

0.04

–0.03/

0.16

–0.03/

0.18

–0.05/

0.12

ns

TISDCK_DDLY_DDR/

TISCKD_DDLY_DDR

D pin Setup/Hold with respect to CLK at DDR mode

(using IODELAY2)

–0.40/

0.48

–0.40/

0.53

–0.40/

0.71

–0.71/

0.86

ns

Sequential Delays

TISCKO_Q

CLKDIV to out at Q pin

1.30

1.44

2.02

2.22

ns

FCLKDIV

CLKDIV maximum frequency

270

262.5

250

125

MHz

Table 38: OSERDES2 Switching Characteristics

Symbol

Description

Speed Grade

Units

-3

-3N

-2

-1L

Setup/Hold

TOSDCK_D/TOSCKD_D

D input Setup/Hold with respect to CLKDIV

–0.03/

1.02

–0.03/

1.17

–0.03/

1.27

–0.02/

0.23

ns

T input Setup/Hold with respect to CLK

–0.05/

1.03

–0.05/

1.13

–0.05/

1.23

–0.05/

0.24

ns

TOSCCK_OCE/TOSCKC_OCE

OCE input Setup/Hold with respect to CLK

0.12/

–0.03

0.15/

–0.03

0.24/

–0.03

0.28/

–0.17

ns

TOSCCK_TCE/TOSCKC_TCE

TCE input Setup/Hold with respect to CLK

0.14/

–0.08

0.17/

–0.08

0.27/

–0.08

0.31/

–0.16

ns

Sequential Delays

TOSCKO_OQ

Clock to out from CLK to OQ

0.94

1.11

1.51

1.89

ns

TOSCKO_TQ

Clock to out from CLK to TQ

0.94

1.11

1.51

1.91

ns

FCLKDIV

CLKDIV maximum frequency

270

262.5

250

125

MHz

Notes:

1.

TOSDCK_T2/TOSCKD_T2 (T input setup/hold with respect to CLKDIV) are reported as TOSDCK_T/TOSCKD_T in TRACE report.

相关PDF资料 |

PDF描述 |

|---|---|

| XC6SLX45T-2FGG484I | IC FPGA SPARTAN 6 43K 484FGGBGA |

| 25LC080D-E/ST | IC SRL EEPROM 1KX8 2.5V 8-TSSOP |

| 25LC080C-E/MS | IC SRL EEPROM 1KX8 2.5V 8-MSOP |

| XC6SLX45T-N3CSG484I | IC FPGA SPARTAN-6 484CSBGA |

| 25AA320AXT-I/ST | IC EEPROM 32KBIT 10MHZ 8TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC6SLX45T-2FGG484C | 功能描述:IC FPGA SPARTAN 6 43K 484FGGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

| XC6SLX45T-2FGG484CES9982 | 制造商:Xilinx 功能描述: |

| XC6SLX45T-2FGG484I | 功能描述:IC FPGA SPARTAN 6 43K 484FGGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC6SLX45T-2FGG676C | 制造商:Xilinx 功能描述: |

| XC6SLX45T-2FGG676I | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。