参数资料

| 型号: | XCV812E-6FG900C |

| 厂商: | Xilinx Inc |

| 文件页数: | 59/118页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V C-TEMP 900-FBGA |

| 产品变化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 标准包装: | 1 |

| 系列: | Virtex®-E EM |

| LAB/CLB数: | 4704 |

| 逻辑元件/单元数: | 21168 |

| RAM 位总计: | 1146880 |

| 输入/输出数: | 556 |

| 门数: | 254016 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 900-BBGA |

| 供应商设备封装: | 900-FBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

DS025-2 (v3.0) March 21, 2014

Module 2 of 4

41

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

HSTL

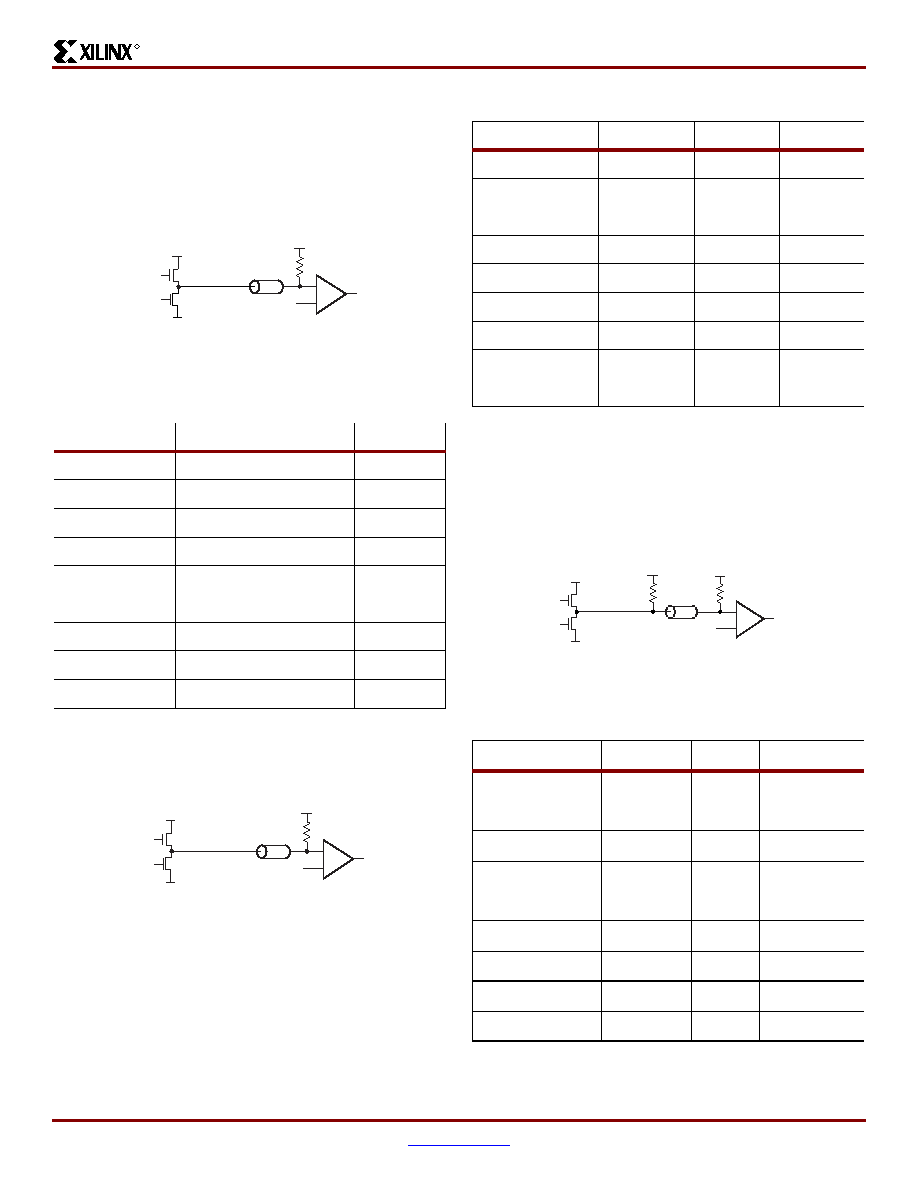

A sample circuit illustrating a valid termination technique for

HSTL_I appears in Figure 46. A sample circuit illustrating a

valid termination technique for HSTL_III appears in

A sample circuit illustrating a valid termination technique for

HSTL_IV appears in Figure 48.

Figure 46: Terminated HSTL Class I

Table 25:

HSTL Class I Voltage Specification

Parameter

Min

Typ

Max

VCCO

1.40

1.50

1.60

VREF

0.68

0.75

0.90

VTT

-VCCO × 0.5

-

VIH

VREF + 0.1

-

VIL

--

VREF – 0.1

VOH

VCCO – 0.4

-

VOL

0.4

IOH at VOH (mA)

8-

-

IOLat VOL (mA)

8

-

Figure 47: Terminated HSTL Class III

VREF = 0.75V

VTT= 0.75V

50

Ω

VCCO = 1.5V

Z = 50

HSTL Class I

x133_10_111699

VREF = 0.9V

VTT= 1.5V

50

Ω

VCCO = 1.5V

Z = 50

HSTL Class III

x133_11_111699

Table 26:

HSTL Class III Voltage Specification

Parameter

Min

Typ

Max

VCCO

1.40

1.50

1.60

VREF (1)

-0.90

-

VTT

-VCCO

-

VIH

VREF + 0.1

-

VIL

--

VREF – 0.1

VOH

VCCO – 0.4

-

VOL

--

0.4

IOH at VOH (mA)

8-

-

IOLat VOL (mA)

24

-

Note: Per EIA/JESD8-6, “The value of VREF is to be selected

by the user to provide optimum noise margin in the use

conditions specified by the user.”

Figure 48: Terminated HSTL Class IV

Table 27:

HSTL Class IV Voltage Specification

Parameter

Min

Typ

Max

VCCO

1.40

1.50

1.60

VREF

-0.90

-

VTT

-VCCO

-

VIH

VREF + 0.1

-

VIL

--

VREF – 0.1

VOH

VCCO – 0.4

-

VOL

--

0.4

IOH at VOH (mA)

8-

-

IOLat VOL (mA)

48

-

Note: Per EIA/JESD8-6, “The value of VREF is to be selected

by the user to provide optimum noise margin in the use

conditions specified by the user.

50

Ω

Z = 50

HSTL Class IV

x133_12_111699

50

Ω

VREF = 0.9V

VTT= 1.5V

VCCO = 1.5V

相关PDF资料 |

PDF描述 |

|---|---|

| RCB106DHAR-S621 | EDGECARD 212POS DIP R/A .050 SLD |

| XC6VLX240T-1FFG1759C | IC FPGA VIRTEX 6 241K 1759FFGBGA |

| ACC65DRXN | CONN EDGECARD 130PS .100 DIP SLD |

| RMC65DRYI-S734 | CONN EDGECARD 130PS DIP .100 SLD |

| XC4VSX55-10FF1148I | IC FPGA VIRTEX-4SX 1148FFBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCV812E-6FG900I | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG404C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG404I | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG556C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG556I | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。