- 您现在的位置:买卖IC网 > PDF目录11830 > XR17C158CV-F (Exar Corporation)IC UART PCI BUS 5V OCTAL 144LQFP PDF资料下载

参数资料

| 型号: | XR17C158CV-F |

| 厂商: | Exar Corporation |

| 文件页数: | 24/67页 |

| 文件大小: | 0K |

| 描述: | IC UART PCI BUS 5V OCTAL 144LQFP |

| 产品培训模块: | UART Product Overview |

| 标准包装: | 60 |

| 特点: | * |

| 通道数: | 8 |

| FIFO's: | 64 字节 |

| 规程: | RS485 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 带自动流量控制功能: | 是 |

| 带IrDA 编码器/解码器: | 是 |

| 带故障启动位检测功能: | 是 |

| 带调制解调器控制功能: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

| 其它名称: | 1016-1287 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页

XR17C158

xr

5V PCI BUS OCTAL UART

REV. 1.4.3

30

4.3

Receiver

The receiver section contains an 8-bit Receive Shift Register (RSR) and Receive Holding Register (RHR). The

RSR uses the 16X or 8X clock for timing. It verifies and validates every bit on the incoming character in the

middle of each data bit. On the falling edge of a start or false start bit, an internal receiver counter starts

counting at the 16X or 8X clock rate. After 8 or 4 clocks the start bit period should be at the center of the start

bit. At this time the start bit is sampled and if it is still a logic 0 it is validated. Evaluating the start bit in this

manner prevents the receiver from assembling a false character. The rest of the data bits and stop bits are

sampled and validated in this same manner to prevent false framing. If there were any error(s), they are

reported in the LSR register bits 1-4. Upon unloading the receive data byte from RHR, the receive FIFO pointer

is bumped and the error flags are immediately updated to reflect the status of the data byte in RHR register.

RHR can generate a receive data ready interrupt upon receiving a character or delay until it reaches the FIFO

trigger level. Furthermore, data delivery to the host is guaranteed by a receive data ready time-out function

when receive data does not reach the receive FIFO trigger level. This time-out delay is 4 word lengths as

defined by LCR[1:0] plus 12 bits time. The RHR interrupt is enabled by IER bit-0.

4.3.1

Receive Holding Register (RHR) - Read-Only

The receive holding register is an 8-bit register that holds a receive data byte from the receive shift register

(RSR). It provides the receive data interface to the host processor. The host reads the receive data byte on this

register whenever a data byte is transferred from the RSR. RHR also part of the receive FIFO of 64 bytes by

11-bit wide, 3 extra bits are for the error flags to be in LSR register. When the FIFO is enabled by FCR bit-0, it

acts as the first-out register of the FIFO as new data are put over the first-in register. The receive FIFO pointer

is bumped after the RHR register is read. Also, the error flags associated with the data byte are immediately

updated onto the line status register (LSR) bits 1-4.

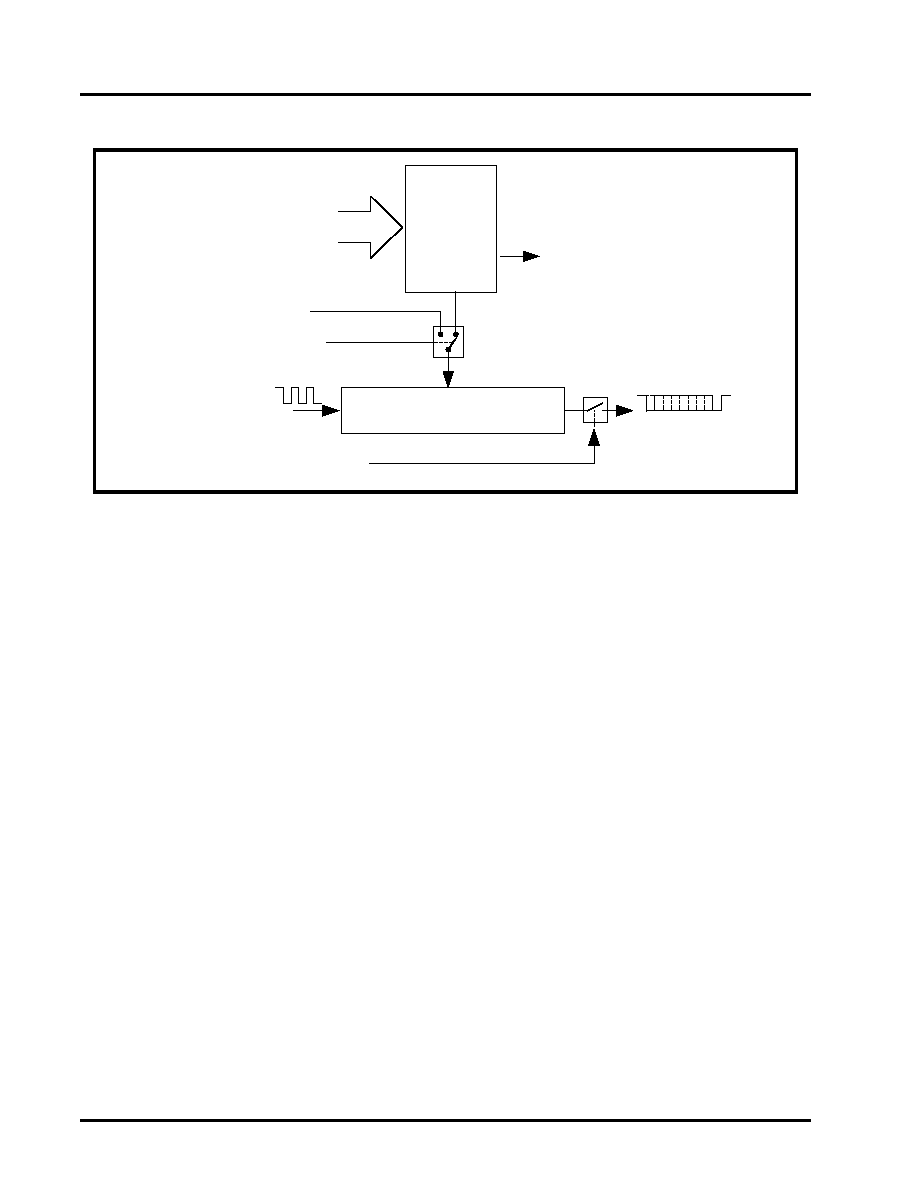

FIGURE 11. TRANSMITTER OPERATION IN FIFO AND FLOW CONTROL MODE

Transmit Data Shift Register

(TSR)

Transmit

Data Byte

THR Interrupt (ISR bit-1) falls

below Programmed Trigger

Level (TXTRG) and then

when becomes empty. FIFO

is Enabled by FCR bit-0=1

Transmit

FIFO

(64-Byte)

TXFIFO1

16X or 8X Clock

(8XMODE Register)

Auto CTS Flow Control (CTS# pin)

Auto Software Flow Control

Flow Control Characters

(Xoff1/2 and Xon1/2 Reg.

相关PDF资料 |

PDF描述 |

|---|---|

| XR17D158CV-F | IC UART PCI BUS OCTAL 144LQFP |

| ATMEGA168-15MZ | MCU AVR 16K FLASH 15MHZ 32-QFN |

| XR17V258IVTR-F | IC UART PCI BUS OCTAL 144LQFP |

| XR16L788IQTR-F | IC UART FIFO 64B OCTAL 100QFP |

| XR17C154IV-F | IC UART PCI BUS QUAD 144LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR17C158CVTR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 64Byte FIFO 5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17C158CVTR-F |

| XR17C158IV | 功能描述:UART 接口集成电路 UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR17C158IV-F | 功能描述:UART 接口集成电路 UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR17C158IVTR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 64Byte FIFO 5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17C158IVTR-F |

| XR17D152 | 制造商:EXAR 制造商全称:EXAR 功能描述:UNIVERSAL (3.3V AND 5V) PCI BUS DUAL UART |

发布紧急采购,3分钟左右您将得到回复。