参数资料

| 型号: | XRM48L950ZWTT |

| 厂商: | Texas Instruments |

| 文件页数: | 160/176页 |

| 文件大小: | 0K |

| 描述: | MCU 16/32Bit FLASH 3MB 337NFBGA |

| 标准包装: | 1 |

| 系列: | Hercules™ ARM® RM4x |

| 应用: | 工业安全,医疗 |

| 核心处理器: | ARM? Cortex? - R4F |

| 程序存储器类型: | 闪存(3MB) |

| 控制器系列: | RM4 |

| RAM 容量: | 256K x 8 |

| 接口: | CAN,以太网,I²C,LIN,MibSPI,SCI,SPI,USB |

| 输入/输出数: | 120 |

| 电源电压: | 1.14 V ~ 3.6 V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 337-LFBGA |

| 包装: | 托盘 |

| 供应商设备封装: | 337-NFBGA(16x16) |

| 其它名称: | 296-29390 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页当前第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页

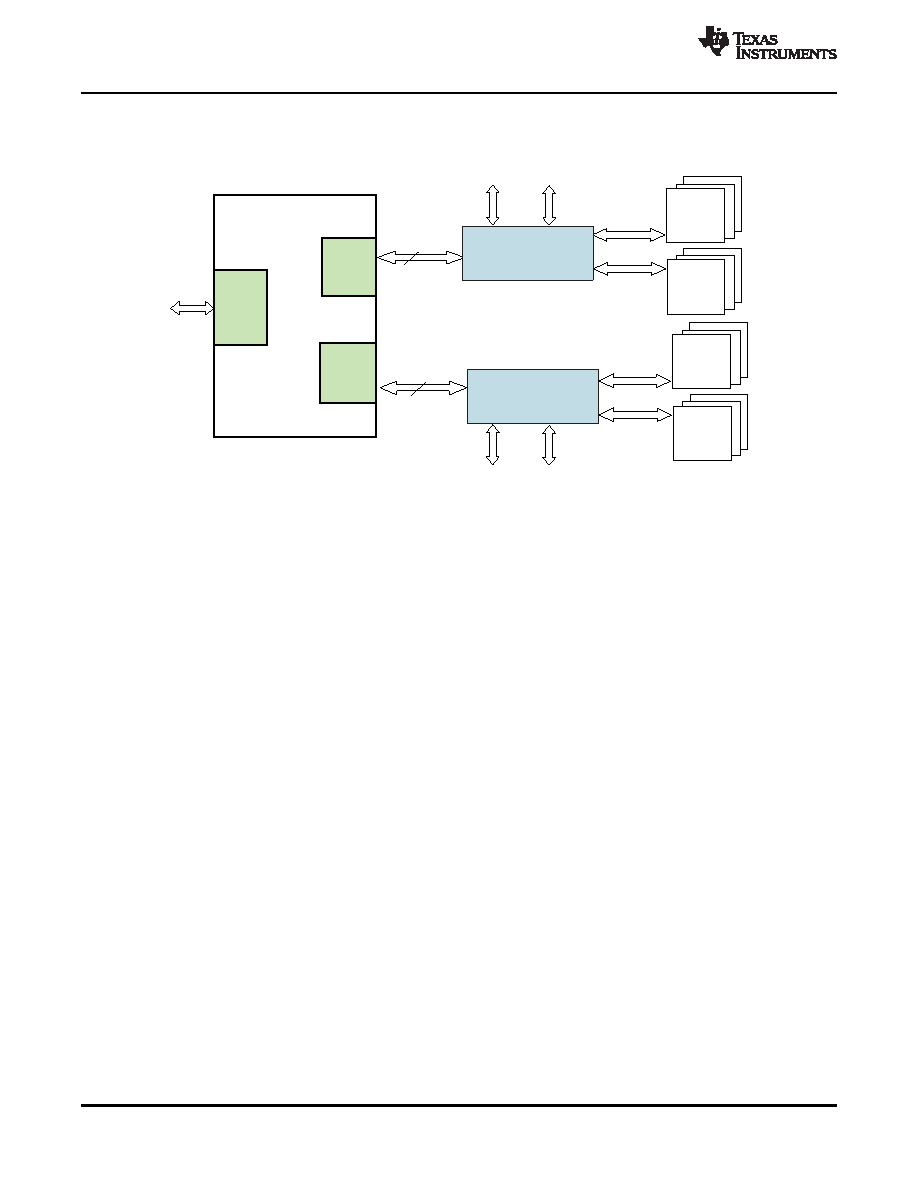

EVEN Address

TCMBUS

ODD Address

TCMBUS

64Bitdatabus

Upper32bits data&

4ECCbits

Lower 32bits data&

4ECCbits

36Bit

wide

RAM

36Bit

wide

RAM

36Bit

wide

RAM

36Bit

wide

RAM

36Bit

wide

RAM

36Bit

wide

RAM

Upper32bits data&

4ECCbits

Lower 32bits data&

4ECCbits

36Bit

wide

RAM

36Bit

wide

RAM

36Bit

wide

RAM

36Bit

wide

RAM

36Bit

wide

RAM

36Bit

wide

RAM

TCRAM

Interface1

PMT I/F

VBUSP I/F

CortexR4F

B0

TCM

B1

TCM

A

TCM

TCRAM

Interface2

PMT I/F

VBUSP I/F

SPNS174A – APRIL 2012 – REVISED SEPTEMBER 2013

4.11 Tightly-Coupled RAM Interface Module

Figure 4-10 illustrates the connection of the Tightly Coupled RAM (TCRAM) to the Cortex-R4F CPU.

Figure 4-10. TCRAM Block Diagram

4.11.1 Features

The features of the Tightly Coupled RAM (TCRAM) Module are:

Acts as slave to the Cortex-R4F CPU's BTCM interface

Supports CPU's internal ECC scheme by providing 64-bit data and 8-bit ECC code

Monitors CPU Event Bus and generates single or multi-bit error interrupts

Stores addresses for single and multi-bit errors

Supports RAM trace module

Provides CPU address bus integrity checking by supporting parity checking on the address bus

Performs redundant address decoding for the RAM bank chip select and ECC select generation logic

Provides enhanced safety for the RAM addressing by implementing two 36-bit wide byte-interleaved

RAM banks and generating independent RAM access control signals to the two banks

Supports auto-initialization of the RAM banks along with the ECC bits

4.11.2 TCRAMW ECC Support

The TCRAMW passes on the ECC code for each data read by the Cortex-R4F CPU from the RAM. It also

stores the CPU's ECC port contents in the ECC RAM when the CPU does a write to the RAM. The

TCRAMW monitors the CPU's event bus and provides registers for indicating single/multi-bit errors and

also for identifying the address that caused the single or multi-bit error. The event signaling and the ECC

checking for the RAM accesses must be enabled inside the CPU.

For more information see the device specific technical reference manual.

4.12

Parity Protection for peripheral RAMs

Most peripheral RAMs are protected by odd/even parity checking. During a read access the parity is

calculated based on the data read from the peripheral RAM and compared with the good parity value

stored in the parity RAM for that peripheral. If any word fails the parity check, the module generates a

parity error signal that is mapped to the Error Signaling Module. The module also captures the peripheral

RAM address that caused the parity error.

84

System Information and Electrical Specifications

Copyright 2012–2013, Texas Instruments Incorporated

相关PDF资料 |

PDF描述 |

|---|---|

| XRT59L91ID-F | IC LIU E1 SGL 3.3V 16SOIC |

| XRT59L921IB | IC LIU E1 21CH 316STBGA |

| XRT72L50IQ-F | IC FRAMER DS3/E3 SGL 100QFP |

| XRT72L52IQTR-F | IC FRAMER DS3/E3 2CH 160QFP |

| XRT72L53IB-F | IC FRAMER DS3/E3 3CH 272PBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRM48L952PGET | 功能描述:ARM微控制器 - MCU 16/32B RISC Fl. MCU RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 处理器系列:STM32F373xx 数据总线宽度:32 bit 最大时钟频率:72 MHz 程序存储器大小:256 KB 数据 RAM 大小:32 KB 片上 ADC:Yes 工作电源电压:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:LQFP-48 安装风格:SMD/SMT |

| XRM48L952ZWTT | 功能描述:ARM微控制器 - MCU 16/32B RISC Fl. MCU RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 处理器系列:STM32F373xx 数据总线宽度:32 bit 最大时钟频率:72 MHz 程序存储器大小:256 KB 数据 RAM 大小:32 KB 片上 ADC:Yes 工作电源电压:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:LQFP-48 安装风格:SMD/SMT |

| XRMQ108D00 | 制造商:TE Connectivity 功能描述: |

| XRMQ208K005+01 | 制造商:TE Connectivity 功能描述: |

| XRMQ208K00501-01 | 制造商:TE Connectivity 功能描述: |

发布紧急采购,3分钟左右您将得到回复。