参数资料

| 型号: | XRT73LC00AIV-F |

| 厂商: | Exar Corporation |

| 文件页数: | 26/61页 |

| 文件大小: | 0K |

| 描述: | IC LIU STS1/DS3/E3 SGL 44TQFP |

| 标准包装: | 160 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 1/1 |

| 规程: | DS3,E3,STS-1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LQFP |

| 供应商设备封装: | 44-TQFP(10x10) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页

XRT73LC00A

29

E3/DS3/STS-1 LINE INTERFACE UNIT

REV. 1.0.2

2.4.2

Disabling the Transmit Line Build-Out Circuit

If the Transmit Line Build-Out circuit is disabled, then the XRT73LC00A outputs partially-shaped pulses onto

the line via the TTIP and TRING output pins.

Disable the Transmit Line Build-Out circuit in the XRT73LC00A by doing the following:

If the XRT73LC00A is operating in the Hardware Mode, set the TXLEV input pin (pin 1) to “High”

If the XRT73LC00A is operating in the HOST Mode, set the TXLEV bit-field to “1” as illustrated below.

2.4.3

Design Guideline for Setting the Transmit Line Build-Out Circuit

The setting ofTXLEV input pin or bit-field should be based upon the overall cable length between the

Transmitting Terminal and the Digital Cross Connect system where the pulse template measurements are

made.

If the cable length between the Transmitting Terminal and the DSX-3 or STSX-1 is less than 225 feet, it is

advisable to enable the Transmit Line Build-Out circuit by setting the TXLEV input pin or bit-field to "0".

NOTE: In this case the XRT73LC00A outputs shaped (e.g., not square-wave) pulses onto the line via the TTIP and TRING

output pins. The shape of this output pulse is such that it complies with the pulse template requirements even

when subjected to cable loss ranging from 0 to 225 feet.

If the cable length between the Transmitting

Terminal and the DSX-3 or STSX-1 is greater than 225 feet, it is advisable to disable the Transmit Line Build-

Out circuit by setting the TXLEV input pin or bit-field to "1".

NOTE: In this case the XRT73LC00A outputs partially-shaped pulses onto the line via the TTIP and TRING output pins.

The cable loss that these pulses experience over long cable lengths (e.g., greater than 225 feet) causes these

pulses to be properly shaped and comply with the appropriate pulse template requirement.

2.4.4

The Transmit Line Build-Out Circuit and E3 Applications

The ITU-T G.703 Pulse Template Requirements for E3 states that the E3 transmit output pulse should be

measured at the Secondary Side of the Transmit Output Transformer for Pulse Template compliance. There is

no Digital Cross Connect System pulse template requirement for E3 and the Transmit Line Build-Out circuit in

the XRT73LC00A is disabled whenever it is operating in the E3 Mode.

2.5

Interfacing the Transmit Section of the XRT73LC00A to the Line

The E3, DS3 and SONET STS-1 specification documents all state that line signals transmitted over coaxial

cable are to be terminated with 75 Ohms. Therefore, interface the Transmit Section of the XRT73LC00A, as

illustrated in Figure 16 which shows two 31.6 Ohm resistors in series with the primary side of the transformer.

These two 31.6Ohm resistors closely match the 75Ohm load termination resistor thereby minimizing Transmit

Return Loss.

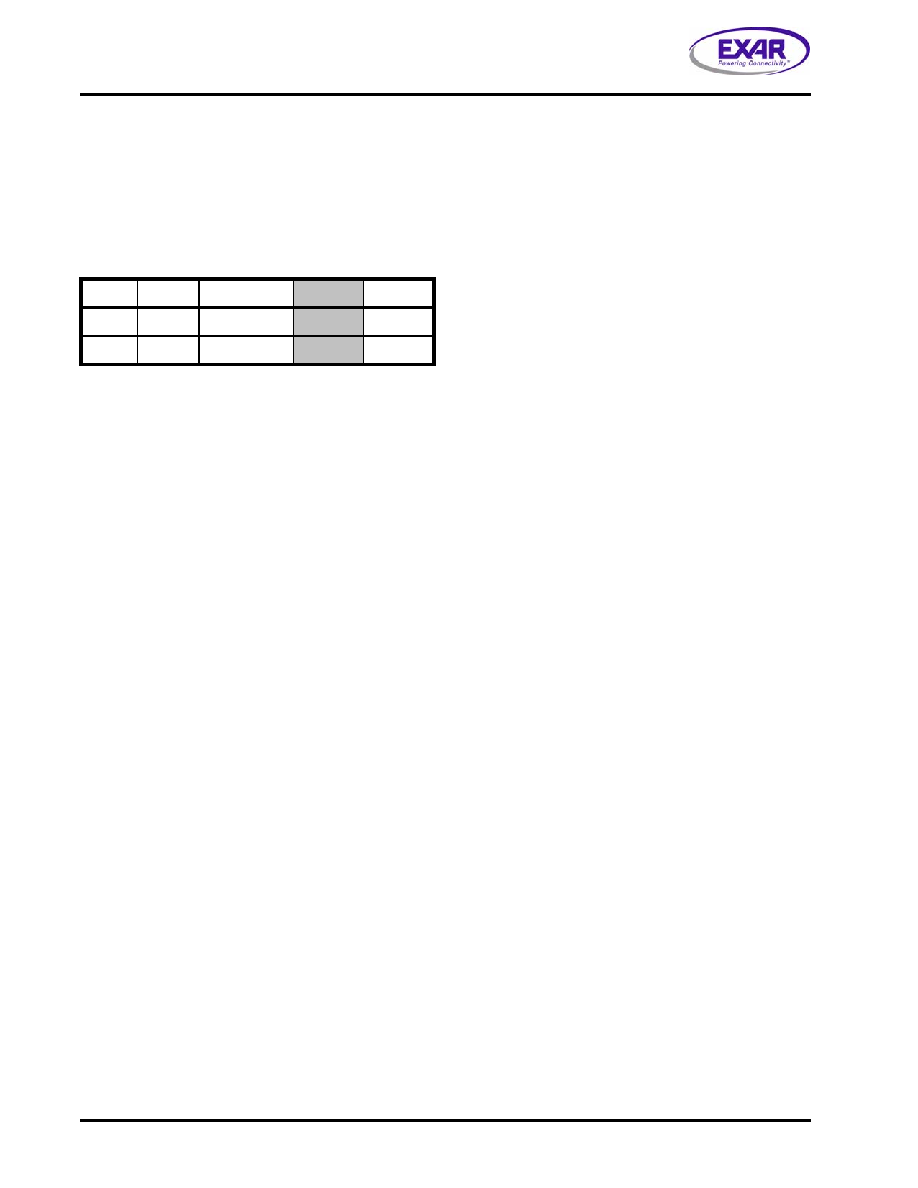

COMMAND REGISTER CR1 (ADDRESS = 0X01)

D4

D3

D2

D1

D0

TXOFF

TAOS

TXCLKINV

TXLEV

TXBIN

0

X

1

X

相关PDF资料 |

PDF描述 |

|---|---|

| XRT73LC03AIV-F | IC LIU E3/DS3/STS-1 3CH 120LQFP |

| XRT73LC04AIV-F | IC LIU E3/DS3/STS-1 4CH 144LQFP |

| XRT73R06IB-F | IC LIU E3/DS3/STS-1 6CH 217BGA |

| XRT73R12IB-L | IC LIU E3/DS3/STS-1 12CH 420TBGA |

| XRT75L00DIV-F | IC LIU E3/DS3/STS-1 SGL 52TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT73LC00AIVTR | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| XRT73LC00AIVTR-F | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| XRT73LC00IV | 制造商:EXAR 制造商全称:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73LC03A | 制造商:EXAR 制造商全称:EXAR 功能描述:3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73LC03A_08 | 制造商:EXAR 制造商全称:EXAR 功能描述:3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

发布紧急采购,3分钟左右您将得到回复。