参数资料

| 型号: | XRT91L34IVTR-F |

| 厂商: | Exar Corporation |

| 文件页数: | 7/38页 |

| 文件大小: | 0K |

| 描述: | IC MULTIRATE CDR QUAD 128LQFP |

| 标准包装: | 750 |

| 类型: | 时钟和数据恢复(CDR),扇出缓冲器(分配),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH,STS,STM |

| 输入: | LVDS,LVPECL |

| 输出: | LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 622.08MHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP |

| 供应商设备封装: | 128-LQFP(14x14) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

XRT91L34

15

REV. 1.0.1

QUAD CHANNEL MULTIRATE STS-12/3/1 AND STM-4/1/0 SONET/SDH CDR

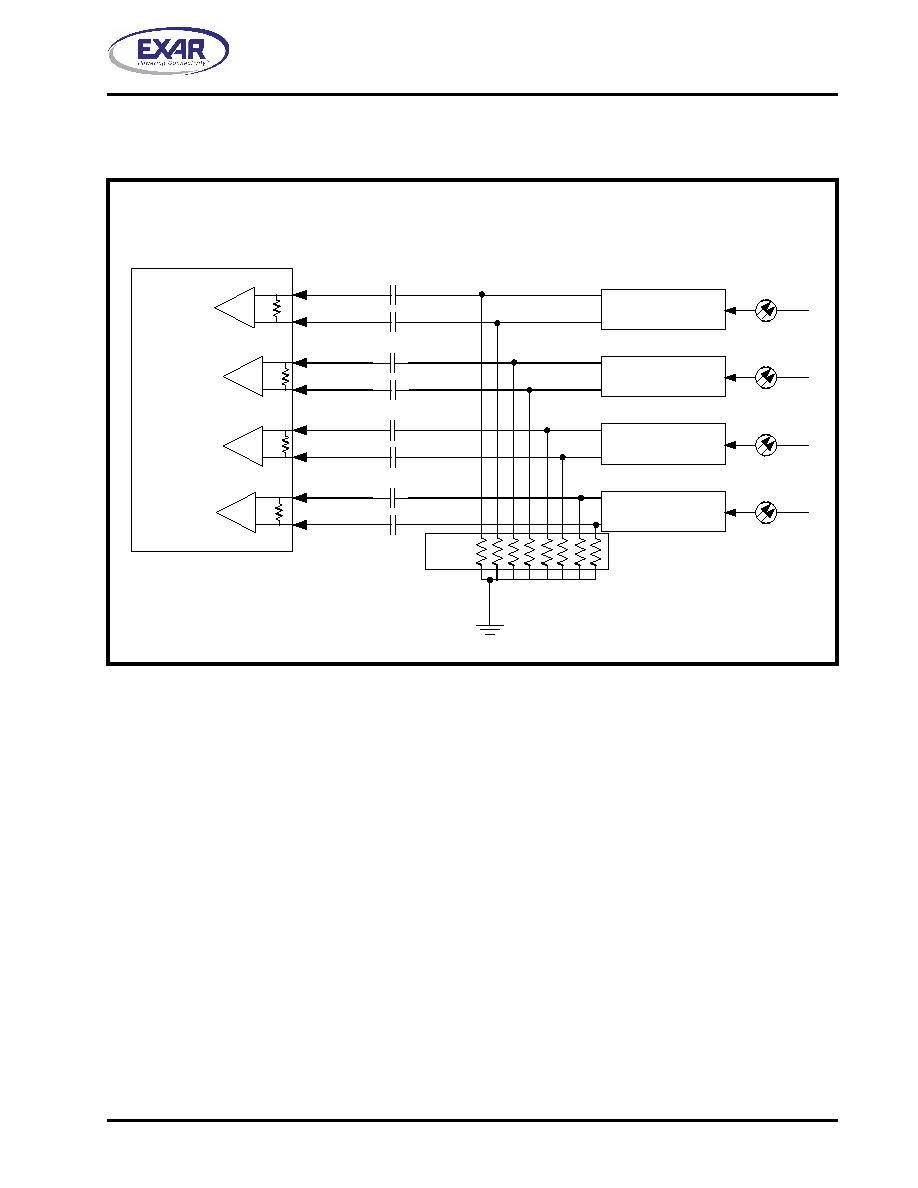

The receive serial inputs can also be AC coupled to an optical module or an electrical interface. A simplified

Differential LVPECL AC coupling using external passive components block diagram is shown in Figure 5.

NOTE: Some optical modules integrate AC coupling capacitors and DC current path resistors internally within the module.

2.2

Receive Clock and Data Recovery

The clock and data recovery (CDR) unit accepts the high speed NRZ serial data from the Differential receiver

and generates a clock that is the same frequency as the incoming data. The clock recovery block utilizes the

reference clock from REFCLKP/N or TTLREFCLK to train and monitor its clock recovery PLL. Upon startup,

the PLL locks to the local reference clock. Once this is achieved, the PLL then attempts to lock onto the

incoming receive serial data stream. Whenever the recovered clock frequency deviates from the local

reference clock frequency by more than approximately ±500 ppm, the clock recovery PLL will switch to the

local reference clock, declare a Loss of Lock and output a high level signal on the LOL output pin. Whenever a

Loss of Lock (LOL) or a Loss of Signal (LOS) event occurs, the CDR will continue to supply a receive clock

(based on the local reference). When the SDEXT becomes active and internal DLOS is cleared and the

recovered clock is determined to be within ±500 ppm accuracy with respect to the local reference source, the

clock recovery PLL will switch back to the incoming receive serial data stream. Table 3 specifies the Clock and

Data Recovery Unit performance characteristics.

FIGURE 5. RECEIVE SERIAL INPUT INTERFACE USING DIFF LVPECL AC COUPLING INTERNAL TERMINATION

Optical Module

RXDI0P

RXDI0N

Optical Fiber

Install DC current path resistors

as close to Optical Module

LVPECL output driver pins

XRT91L34

STS-12/3/1

or

STM-4/1/0

Clock and Data

Recovery

RXDI1P

RXDI1N

RXDI2P

RXDI2N

RXDI3P

RXDI3N

Optical Module

Optical Fiber

Optical Module

Optical Fiber

Optical Module

Optical Fiber

Channel 0

Channel 1

Channel 2

Channel 3

DIFF LVPECL A/C Coupling using

External Passive Components

130 x 8

100

VBB1.2

Internal 100 Ohm line-to-line

termination active on

RXDI[3:0]P and RXDI[3:0]N pins

相关PDF资料 |

PDF描述 |

|---|---|

| VI-210-MX-F3 | CONVERTER MOD DC/DC 5V 75W |

| VI-J4D-MX-F3 | CONVERTER MOD DC/DC 85V 75W |

| VI-J4D-MX-F2 | CONVERTER MOD DC/DC 85V 75W |

| VI-J4D-MX-F1 | CONVERTER MOD DC/DC 85V 75W |

| VI-J4B-MX-F4 | CONVERTER MOD DC/DC 95V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT91L80 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L80_0507 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L80ES | 功能描述:总线收发器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| XRT91L80IB | 功能描述:总线收发器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| XRT91L80IB-F | 功能描述:总线收发器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。