- 您现在的位置:买卖IC网 > PDF目录67338 > 5962-9561501MLX (ANALOG DEVICES INC) 8-CH 12-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, CDIP24 PDF资料下载

参数资料

| 型号: | 5962-9561501MLX |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | ADC |

| 英文描述: | 8-CH 12-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, CDIP24 |

| 封装: | 0.300 INCH, HERMETIC SEALED, CERDIP-24 |

| 文件页数: | 17/22页 |

| 文件大小: | 203K |

| 代理商: | 5962-9561501MLX |

REV. B

AD7890

–4–

TIMING CHARACTERISTICS1, 2

Limit at TMIN, TMAX

Parameter

(A, B, S Versions)

Unit

Conditions/Comments

fCLKIN

3

100

kHz min

Master Clock Frequency. For Specified Performance

2.5

MHz max

tCLK IN LO

0.3

× t

CLK IN

ns min

Master Clock Input Low Time

tCLK IN HI

0 3

× t

CLK IN

ns min

Master Clock Input High Time

tr

4

25

ns max

Digital Output Rise Time. Typically 10 ns

tf

4

25

ns max

Digital Output Fall Time. Typically 10 ns

tCONVERT

5.9

s max

Conversion Time

tCST

100

ns min

CONVST Pulsewidth

Self-Clocking Mode

t1

tCLK IN HI + 50

ns max

RFS Low to SCLK Falling Edge

t2

5

25

ns max

RFS Low to Data Valid Delay

t3

tCLK IN HI

ns nom

SCLK High Pulsewidth

t4

tCLK IN LO

ns nom

SCLK Low Pulsewidth

t5

5

20

ns max

SCLK Rising Edge to Data Valid Delay

t6

40

ns max

SCLK Rising Edge to

RFS Delay

t7

6

50

ns max

Bus Relinquish Time after Rising Edge of SCLK

t8

0

ns min

TFS Low to SCLK Falling Edge

tCLK IN + 50

ns max

t9

0

ns min

Data Valid to

TFS Falling Edge Setup Time (A2 Address Bit)

t10

20

ns min

Data Valid to SCLK Falling Edge Setup Time

t11

10

ns min

Data Valid to SCLK Falling Edge Hold Time

t12

20

ns min

TFS to SCLK Falling Edge Hold Time

External-Clocking Mode

t13

20

ns min

RFS Low to SCLK Falling Edge Setup Time

t14

5

40

ns max

RFS Low to Data Valid Delay

t15

50

ns min

SCLK High Pulsewidth

t16

50

ns min

SCLK Low Pulsewidth

t17

5

35

ns max

SCLK Rising Edge to Data Valid Delay

t18

20

ns min

RFS to SCLK Falling Edge Hold Time

t19

6

50

ns max

Bus Relinquish Time after Rising Edge of

RFS

t19A

6

90

ns max

Bus Relinquish Time after Rising Edge of SCLK

t20

20

ns min

TFS Low to SCLK Falling Edge Setup Time

t21

10

ns min

Data Valid to SCLK Falling Edge Setup Time

t22

15

ns min

Data Valid to SCLK Falling Edge Hold Time

t23

40

ns min

TFS to SCLK Falling Edge Hold Time

NOTES

1Sample tested at –25

°C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

2See Figures 8 to 11.

3The AD7890 is production tested with f

CLK IN at 2.5 MHz. It is guaranteed by characterization to operate at 100 kHz.

4Specified using 10% and 90% points on waveform of interest.

5These numbers are measured with the load circuit of Figure 1 and defined as the time required for the output to cross 0.8 V or 2.4 V.

6These numbers are derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then

extrapolated back to remove effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the tim ing characteristics are the true bus

relinquish times of the part and as such are independent of external bus loading capacitances.

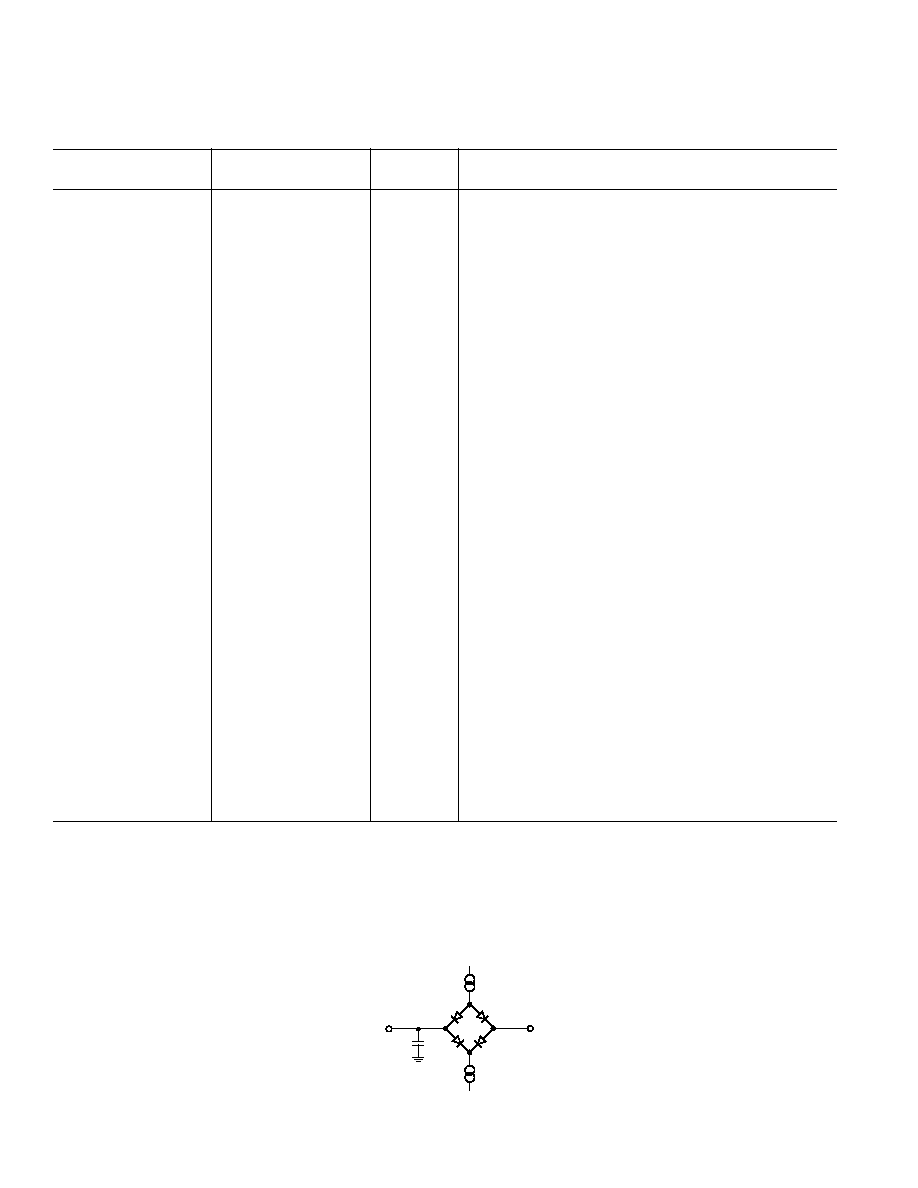

TO OUTPUT

PIN

+2.1V

1.6mA

200 A

50pF

Figure 1. Load Circuit for Access Time and Bus Relinquish Time

(VDD = 5 V

5%, AGND = DGND = 0 V, REF IN = 2.5 V, fCLK IN = 2.5 MHz external, MUX OUT

connected to SHA IN.)

相关PDF资料 |

PDF描述 |

|---|---|

| 5962-9562301QXA | 16-CHANNEL, SGL ENDED MULTIPLEXER, CDIP28 |

| 5962-9562302QXA | 8-CHANNEL, DIFFERENTIAL MULTIPLEXER, CDIP28 |

| 5962-9562302QXA | 8-CHANNEL, DIFFERENTIAL MULTIPLEXER, CDIP28 |

| 5962-9566702MEX | DUAL, SERIAL INPUT LOADING, 12-BIT DAC, CDIP16 |

| 5962-9566701MEX | DUAL, SERIAL INPUT LOADING, 12-BIT DAC, CDIP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962-9562302Q2A | 制造商:Vishay Siliconix 功能描述:DUAL MARKED - DG407AZ/883 - Rail/Tube |

| 5962-9562901QCA | 制造商:Vishay Siliconix 功能描述:ANLG SW DUAL SPST 22V/36V 14CDIP - Rail/Tube |

| 5962-9563301Q2A | 制造商:Texas Instruments 功能描述:Pref DRVR Dual 4.5V to 5.5V 1375mW 20-Pin LCCC Tube 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 5962-9563301QPA | 制造商:Texas Instruments 功能描述:Pref DRVR Dual 4.5V to 5.5V 1050mW 8-Pin CDIP Tube 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 59629563901MGA | 制造商:AD 功能描述:AMP038JMD |

发布紧急采购,3分钟左右您将得到回复。