- 您现在的位置:买卖IC网 > PDF目录122717 > 9UMS9633BKLFT (INTEGRATED DEVICE TECHNOLOGY INC) 166.67 MHz, OTHER CLOCK GENERATOR, PQCC48 PDF资料下载

参数资料

| 型号: | 9UMS9633BKLFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 166.67 MHz, OTHER CLOCK GENERATOR, PQCC48 |

| 封装: | 6 X 6 MM, 0.40 MM PITCH, ROHS COMPLIANT, PLASTIC, MLF-48 |

| 文件页数: | 18/22页 |

| 文件大小: | 208K |

| 代理商: | 9UMS9633BKLFT |

IDTTM/ICSTM Ultra Mobile PC/Mobile Internet Device

1423—01/20/09

ICS9UMS9633B

ULTRA MOBILE PC/MOBILE INTERNET DEVICE

5

Advance Information

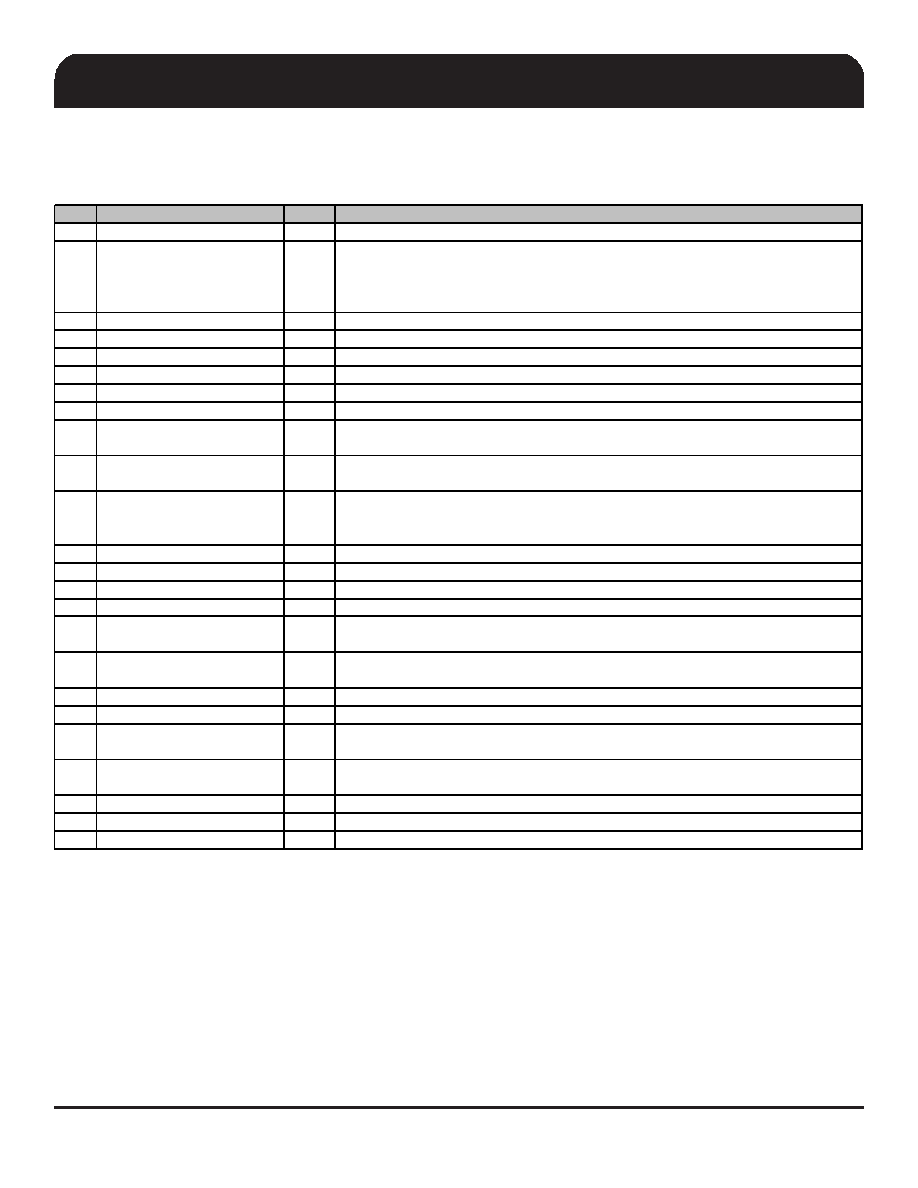

MLF Pin Description

PIN #

PIN NAME

TYPE

DESCRIPTION

1

CPU_STOP#

IN

Stops all CPU clocks, except those set to be free running clocks

2

CLKPWRGD#/PD_3.3

IN

This 3.3V LVTTL input is a level sensitive strobe used to determine when latch inputs

are valid and are ready to be sampled. This is an active low input. / Asynchronous

active high input pin used to place the device into a power down state.

3X2

OUT

Crystal output, Nominally 14.318MHz

4

X1

IN

Crystal input, Nominally 14.318MHz.

5

VDDREF_3.3

PWR Power pin for the XTAL and REF clocks, nominal 3.3V

6

REF

OUT

14.318 MHz reference clock.

7

GNDREF

PWR Ground pin for the REF outputs.

8

VDDCORE_3.3

PWR 3.3V power for the PLL core

9FSC_L

IN

Low threshold input for CPU frequency selection. Refer to input electrical

characteristics for Vil_FS and Vih_FS values.

10

TEST_MODE

IN

TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode

while in test mode. Refer to Test Clarification Table.

11

TEST_SEL

IN

TEST_SEL: latched input to select TEST MODE

1 = All outputs are tri-stated for test

0 = All outputs behave normally.

12

SCLK_3.3

IN

Clock pin of SMBus circuitry, 3.3V tolerant.

13

SDATA_3.3

I/O

Data pin for SMBus circuitry, 3.3V tolerant.

14

VDDCORE_3.3

PWR 3.3V power for the PLL core

15

VDDIO_1.5

PWR Power supply for low power differential outputs, nominal 1.5V.

16

DOT96C_LPR

OUT

Complement clock of low power differential pair for 96.00MHz DOT clock. No 50ohm

resistor to GND needed. No Rs needed.

17

DOT96T_LPR

OUT

True clock of low power differential pair for 96.00MHz DOT clock. No 50ohm resistor

to GND needed. No Rs needed.

18

GNDDOT

PWR Ground pin for DOT clock output

19

GNDLCD

PWR Ground pin for LCD clock output

20

LCD100C_LPR

OUT

Complement clock of low power differential pair for LCD100 SS clock. No 50ohm

resistor to GND needed. No Rs needed.

21

LCD100T_LPR

OUT

True clock of low power differential pair for LCD100 SS clock. No 50ohm resistor to

GND needed. No Rs needed.

22

VDDIO_1.5

PWR Power supply for low power differential outputs, nominal 1.5V.

23

VDDCORE_3.3

PWR 3.3V power for the PLL core

24

*CR#0

IN

Clock request for SRC0, 0 = enable, 1 = disable

相关PDF资料 |

PDF描述 |

|---|---|

| 935263686518 | 6 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, PQFP64 |

| 9154A-04CS16 | 100 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| 9212AF-13 | 533.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO24 |

| 9248BF-138LF | 166.67 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 9250BF-28LF-T | 133.32 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9US99/25917 | 制造商:MCM 功能描述:CHEMICAL SPILL KIT LAB SAFETY 制造商:Distributed By MCM 功能描述:Lab Safety Chemical Spill Kit |

| 9US99/8UKR2 | 制造商:MCM 功能描述:CHEMICAL SPILL KIT LAB SAFETY |

| 9UWE0300000 | 制造商:LG Corporation 功能描述:SOLDER,SOLDERING |

| 9V HR 22 12X1=12 | 制造商:Energizer 功能描述:Bulk |

| 9V POWER PACK | 功能描述:POWER SUPPLY 9V FOR DESIGN HDWR RoHS:否 类别:编程器,开发系统 >> 配件 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program RoHS指令信息:IButton RoHS Compliance Plan 标准包装:1 系列:- 附件类型:USB 至 1-Wire? RJ11 适配器 适用于相关产品:1-Wire? 设备 产品目录页面:1429 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。