- 您现在的位置:买卖IC网 > PDF目录253905 > A3P015-1QNG68I FPGA, 384 CLBS, 15000 GATES, QCC68 PDF资料下载

参数资料

| 型号: | A3P015-1QNG68I |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 384 CLBS, 15000 GATES, QCC68 |

| 封装: | 8 X 8 MM, 0.90 MM HEIGHT, 0.40 MM PITCH, GREEN, QFN-68 |

| 文件页数: | 149/218页 |

| 文件大小: | 6270K |

| 代理商: | A3P015-1QNG68I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页当前第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页

ProASIC3 DC and Switching Characteristics

2- 22

v1.4

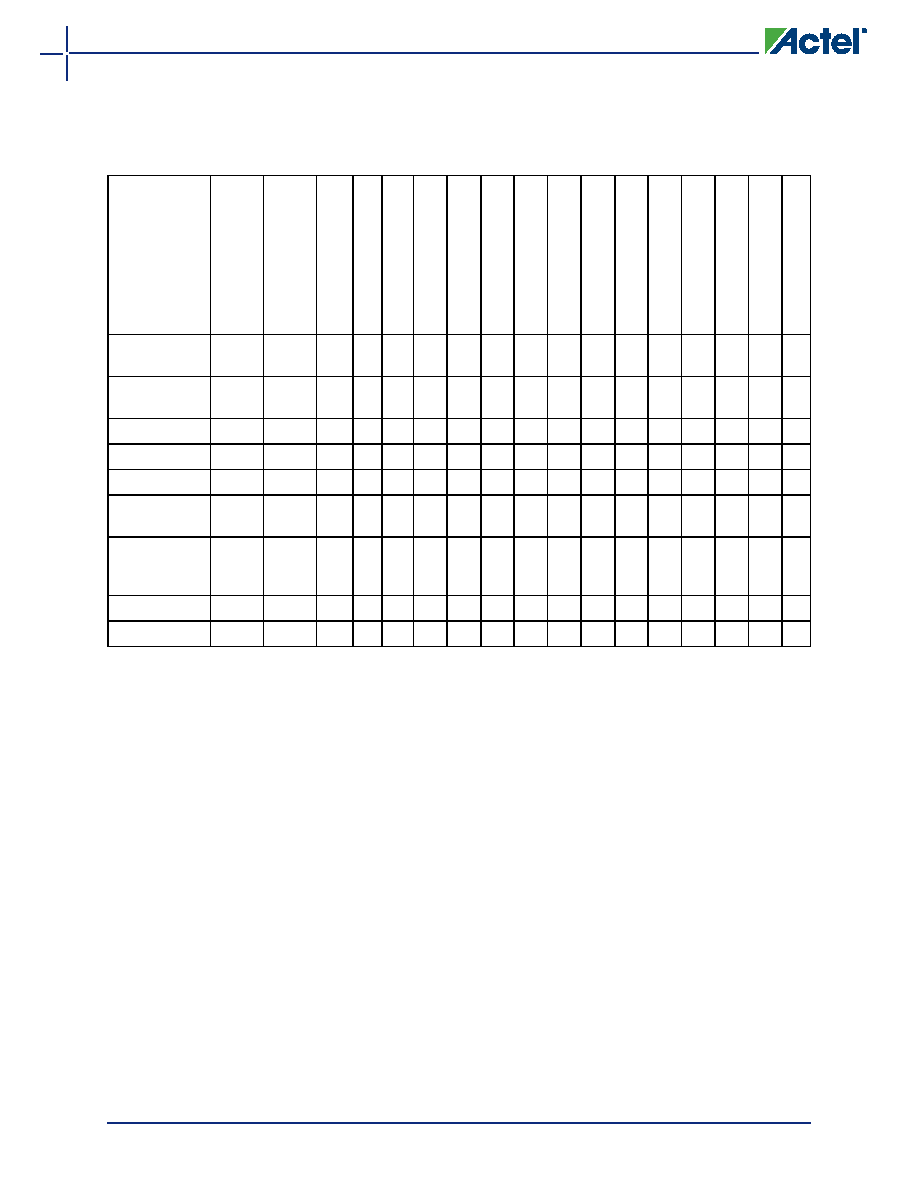

Table 2-24 Summary of I/O Timing Characteristics—Software Default Settings

–2 Speed Grade, Commercial-Case Conditions: TJ = 70°C, Worst Case VCC = 1.425 V,

Worst-Case VCCI (per standard)

Advanced I/O Banks

I/O Standard

D

ri

v

e

St

re

n

g

th

Equiv

.Softwa

re

Def

a

ult

D

riv

e

Str

e

ngth

Option

1

Slew

Rate

Capacitive

Load

(pF)

Ex

ter

n

al

Res

is

tor

(Ω

)

t DO

UT

(ns)

t DP

(ns)

t DI

N

(ns)

t PY

(n

s)

t EO

UT

(ns)

t ZL

(n

s)

t ZH

(ns)

t LZ

(n

s)

t HZ

(ns)

t ZLS

(ns)

t ZH

S

(ns)

Unit

s

3.3 V LVTTL /

3.3 V LVCMOS

12 mA 12 mA High 35

–

0.45 2.64 0.03 0.76 0.32 2.69 2.11 2.40 2.68 4.36 3.78

ns

3.3 V LVCMOS

Wide Range2

100 A 12 mA High 35

–

0.45 4.08 0.03 0.76 0.32 4.08 3.20 3.71 4.14 6.61 5.74

ns

2.5 V LVCMOS

12 mA 12 mA High 35

–

0.45 2.66 0.03 0.98 0.32 2.71 2.56 2.47 2.57 4.38 4.23

ns

1.8 V LVCMOS

12 mA 12 mA High 35

–

0.45 2.64 0.03 0.91 0.32 2.69 2.27 2.76 3.05 4.36 3.94

ns

1.5 V LVCMOS

12 mA 12 mA High 35

–

0.45 3.05 0.03 1.07 0.32 3.10 2.67 2.95 3.14 4.77 4.34

ns

3.3 V PCI

Per PCI

spec

–

High 10 25 4 0.45 2.00 0.03 0.65 0.32 2.04 1.46 2.40 2.68 3.71 3.13

ns

3.3 V PCI-X

Per

PCI-X

spec

–

High 10 25 4 0.45 2.00 0.03 0.62 0.32 2.04 1.46 2.40 2.68 3.71 3.13

ns

LVDS

24 mA

–

High

–

0.45 1.37 0.03 1.20

–

ns

LVPECL

24 mA

–

High

–

0.45 1.34 0.03 1.05

–

ns

Notes:

1. Please note that 3.3 V LVCMOS wide range is applicable to 100 A drive strength only. The configuration

will NOT operate at the equivalent software default drive strength. These values are for Normal Ranges

ONLY.

2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8b

specification.

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.

4. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-10 on

page 2-66 for connectivity. This resistor is not required during normal operation.

相关PDF资料 |

PDF描述 |

|---|---|

| A3P015-1QNG68 | FPGA, 384 CLBS, 15000 GATES, 350 MHz, QCC68 |

| A3P015-2QN68I | FPGA, 384 CLBS, 15000 GATES, QCC68 |

| A3P015-2QN68 | FPGA, 384 CLBS, 15000 GATES, 350 MHz, QCC68 |

| A3P015-2QNG68I | FPGA, 384 CLBS, 15000 GATES, QCC68 |

| A3P015-2QNG68 | FPGA, 384 CLBS, 15000 GATES, 350 MHz, QCC68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A3P015-1VQ144 | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P015-1VQ144ES | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P015-1VQ144I | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P015-1VQ144PP | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P015-1VQG144 | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

发布紧急采购,3分钟左右您将得到回复。