- 您现在的位置:买卖IC网 > PDF目录379534 > A54SX08P-PQ208M (Electronic Theatre Controls, Inc.) 54SX Family FPGAs PDF资料下载

参数资料

| 型号: | A54SX08P-PQ208M |

| 厂商: | Electronic Theatre Controls, Inc. |

| 元件分类: | FPGA |

| 英文描述: | 54SX Family FPGAs |

| 中文描述: | 54SX家庭的FPGA |

| 文件页数: | 4/57页 |

| 文件大小: | 415K |

| 代理商: | A54SX08P-PQ208M |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页

5 4 S X F a m ily F P G A s

4

v3.1

S X F a m ily A rc hit e c t ure

The SX family architecture was designed to satisfy

next-generation performance and integration requirements

for production-volume designs in a broad range of

applications.

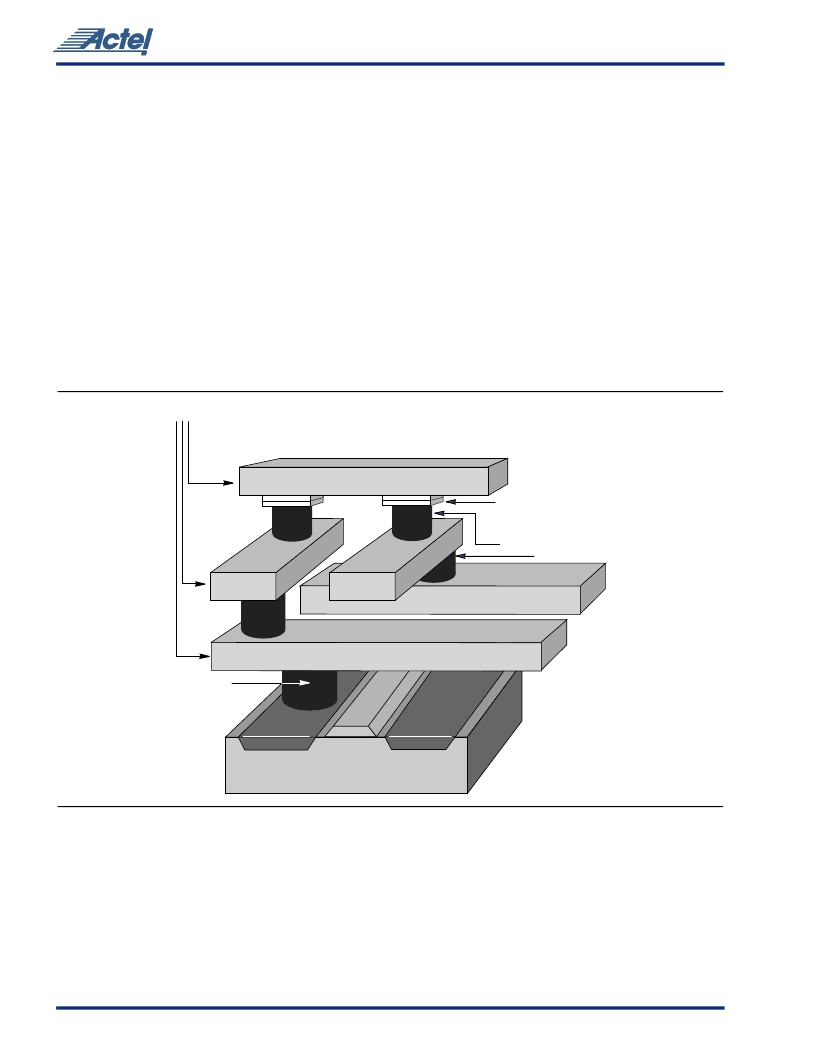

P rog ra m m a ble Int e rc onne c t E le m e nt

The SX family provides efficient use of silicon by locating the

routing interconnect resources between the Metal 2 (M2)

and Metal 3 (M3) layers (

Figure1

). This completely

eliminates the channels of routing and interconnect

resources between logic modules (as implemented on SRAM

FPGAs and previous generations of antifuse FPGAs), and

enables the entire floor of the device to be spanned with an

uninterrupted grid of logic modules.

Interconnection between these logic modules is achieved

using Actel’s patented metal-to-metal programmable

antifuse interconnect elements, which are embedded

between the M2 and M3 layers. The antifuses are normally

open circuit and, when programmed, form a permanent

low-impedance connection.

The extremely small size of these interconnect elements

gives the SX family abundant routing resources and provides

excellent protection against design pirating. Reverse

engineering is virtually impossible because it is extremely

difficult to distinguish between programmed and

unprogrammed antifuses, and there is no configuration

bitstream to intercept.

Additionally, the interconnect (i.e., the antifuses and metal

tracks) have lower capacitance and lower resistance than

any other device of similar capacity, leading to the fastest

signal propagation in the industry.

L og ic Module D e s ig n

The SX family architecture is described as a

“sea-of-modules” architecture because the entire floor of

the device is covered with a grid of logic modules with

virtually no chip area lost to interconnect elements or

routing. Actel’s SX family provides two types of logic

modules, the register cell (R-cell) and the combinatorial

cell (C-cell).

The R-cell contains a flip-flop featuring asynchronous clear,

asynchronous preset, and clock enable (using the S0 and S1

lines) control signals (

Figure2 on page5

). The R-cell

registers feature programmable clock polarity selectable on

a register-by-register basis. This provides additional

flexibility while allowing mapping of synthesized functions

into the SX FPGA. The clock source for the R-cell can be

chosen from either the hard-wired clock or the routed clock.

Figure 1

SX Family Interconnect Elements

Silicon Substrate

Tungsten Plug

Contact

Metal 1

Metal 2

Metal 3

Routing Tracks

Amorphous Silicon/

Dielectric Antifuse

Tungsten Plug Via

Tungsten Plug Via

相关PDF资料 |

PDF描述 |

|---|---|

| A54SX08P-PQ208PP | LM1881 Video Sync Separator; Package: SOIC NARROW; No of Pins: 8 |

| A54SX08P-TQ208 | LM1881 Video Sync Separator; Package: MDIP; No of Pins: 8; Qty per Container: 40; Container: Rail |

| A54SX08P-TQ208I | LM1894 Dynamic Noise Reduction System DNR®; Package: SOIC NARROW; No of Pins: 14; Qty per Container: 55; Container: Rail |

| A54SX08P-TQ208M | 54SX Family FPGAs |

| A54SX08P-TQ208PP | 54SX Family FPGAs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A54SX08P-PQ208PP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:54SX Family FPGAs |

| A54SX08-PQ208 | 功能描述:IC FPGA SX 12K GATES 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:SX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A54SX08-PQ208I | 功能描述:IC FPGA SX 12K GATES 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:SX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A54SX08-PQ208M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:54SX Family FPGAs |

| A54SX08-PQ208PP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:54SX Family FPGAs |

发布紧急采购,3分钟左右您将得到回复。