- 您现在的位置:买卖IC网 > PDF目录1891 > AD5933YRSZ-REEL7 (Analog Devices Inc)NETWORK ANALYZER 12B 1MSP 16SSOP PDF资料下载

参数资料

| 型号: | AD5933YRSZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 37/40页 |

| 文件大小: | 0K |

| 描述: | NETWORK ANALYZER 12B 1MSP 16SSOP |

| 产品培训模块: | AD5933 Impedance to Digital Converter Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 标准包装: | 500 |

| 分辨率(位): | 12 b |

| 主 fclk: | 16.776MHz |

| 电源电压: | 2.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 16-SSOP |

| 包装: | 带卷 (TR) |

| 配用: | EVAL-AD5933EBZ-ND - BOARD EVALUATION FOR AD5933 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页

AD5933

Data Sheet

Rev. E | Page 6 of 40

I2C SERIAL INTERFACE TIMING CHARACTERISTICS

Table 2.

Parameter2

Limit at TMIN, TMAX

Unit

Description

fSCL

400

kHz max

SCL clock frequency

t1

2.5

μs min

SCL cycle time

t2

0.6

μs min

tHIGH, SCL high time

t3

1.3

μs min

tLOW, SCL low time

t4

0.6

μs min

tHD, STA, start/repeated start condition hold time

t5

100

ns min

tSU, DAT, data setup time

0.9

μs max

tHD, DAT, data hold time

0

μs min

tHD, DAT, data hold time

t7

0.6

μs min

tSU, STA, setup time for repeated start

t8

0.6

μs min

tSU, STO, stop condition setup time

t9

1.3

μs min

tBUF, bus free time between a stop and a start condition

t10

300

ns max

tF, rise time of SDA when transmitting

0

ns min

tR, rise time of SCL and SDA when receiving (CMOS compatible)

t11

300

ns max

tF, fall time of SCL and SDA when transmitting

0

ns min

tF, fall time of SDA when receiving (CMOS compatible)

250

ns max

tF, fall time of SDA when receiving

20 + 0.1 Cb4

ns min

tF, fall time of SCL and SDA when transmitting

Cb

400

pF max

Capacitive load for each bus line

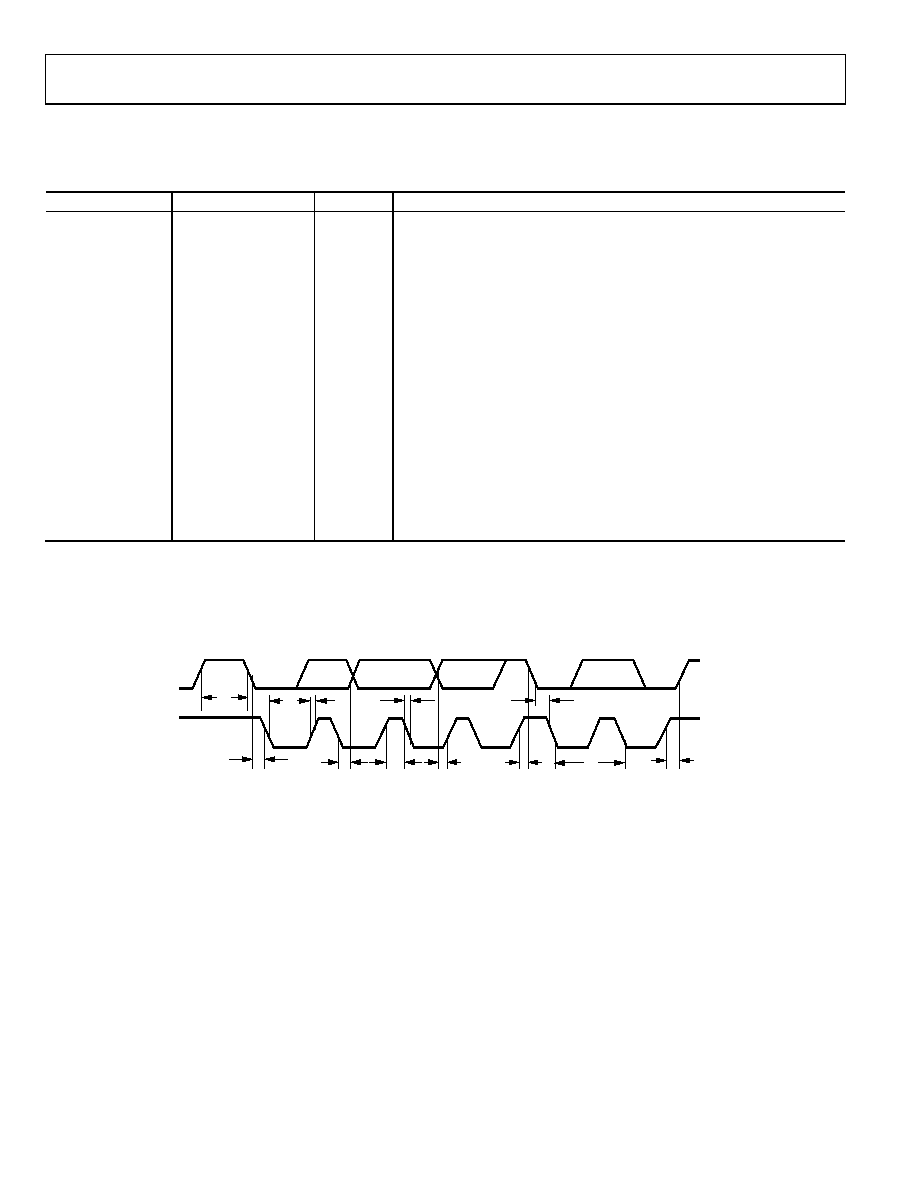

1 See Figure 2.

2 Guaranteed by design and characterization, not production tested.

3 A master device must provide a hold time of at least 300 ns for the SDA signal (referred to VIH MIN of the SCL signal) to bridge the undefined falling edge of SCL.

4 Cb is the total capacitance of one bus line in picofarads. Note that tR and tF are measured between 0.3 VDD and 0.7 VDD.

SCL

SDA

t9

t3

t10

t11

t4

t6

t2

t5

t7

t8

t1

05

32

4-

0

02

START

CONDITION

REPEATED

START

CONDITION

STOP

CONDITION

Figure 2. I2C Interface Timing Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| AD5934YRSZ | IC NTWK ANALYZER 12B 1MSP 16SSOP |

| AD598JR | IC LVDT SGNL COND OSC/REF 20SOIC |

| AD660BR | IC DAC 16BIT MONO W/VREF 24-SOIC |

| AD6620ASZ | IC DGTL RCVR DUAL 67MSPS 80-PQFP |

| AD6623ASZ | IC TSP 4CHAN 104MSPS 128MQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5934 | 制造商:Analog Devices 功能描述:IMPEDANCE TO DIGITAL CONVERTERS - Bulk |

| AD5934YRSZ | 功能描述:IC NTWK ANALYZER 12B 1MSP 16SSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD5934YRSZ-REEL7 | 功能描述:IC CONV 12BIT 250KSPS 16SSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 直接数字合成 (DDS) 系列:- 产品变化通告:Product Discontinuance 27/Oct/2011 标准包装:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 调节字宽(位):32 b 电源电压:2.97 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD594 | 制造商:AD 制造商全称:Analog Devices 功能描述:Monolithic Thermocouple Amplifiers with Cold Junction Compensation |

| AD594A | 制造商:AD 制造商全称:Analog Devices 功能描述:Monolithic Thermocouple Amplifiers with Cold Junction Compensation |

发布紧急采购,3分钟左右您将得到回复。