- 您现在的位置:买卖IC网 > PDF目录373890 > AD6620S (Analog Devices, Inc.) 65 MSPS Digital Receive Signal Processor PDF资料下载

参数资料

| 型号: | AD6620S |

| 厂商: | Analog Devices, Inc. |

| 英文描述: | 65 MSPS Digital Receive Signal Processor |

| 中文描述: | 65 MSPS的数字接收信号处理器 |

| 文件页数: | 3/43页 |

| 文件大小: | 354K |

| 代理商: | AD6620S |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页

AD6620

–3–

REV. 0

Following CIC2 is the second fixed-coefficient decimating filter.

This filter, CIC5, further reduces the sample rate by a program-

mable ratio from 1 to 32. The data rate out of CIC5, f

SAMP5

, is

determined by the decimation factors of M

CIC5

and M

CIC2

.

Each CIC stage is a FIR filter whose response is defined by the

decimation rate. The purpose of these filters is to reduce the

data rate of the incoming signal so that the final filter stage, a

FIR RAM coefficient sum-of-products filter (RCF), can calcu-

late more taps per output. As shown in Figure 1, on-chip multi-

plexers allow both CIC filters to be bypassed if a multirate clock

is used.

The fourth stage is a sum-of-products FIR filter with program-

mable 20-bit coefficients, and decimation rates programmable

from 1 to 32. The RAM Coefficient FIR Filter (RCF in Figure

1) can handle a maximum of 256 taps.

The overall filter response for the AD6620 is the composite of

all three cascaded decimating filters: CIC2, CIC5, and RCF.

Each successive filter stage is capable of narrower transition

bandwidths but requires a greater number of CLK cycles to

calculate the output. More decimation in the first filter stage will

minimize overall power consumption. Data comes out via a

parallel port or a serial interface.

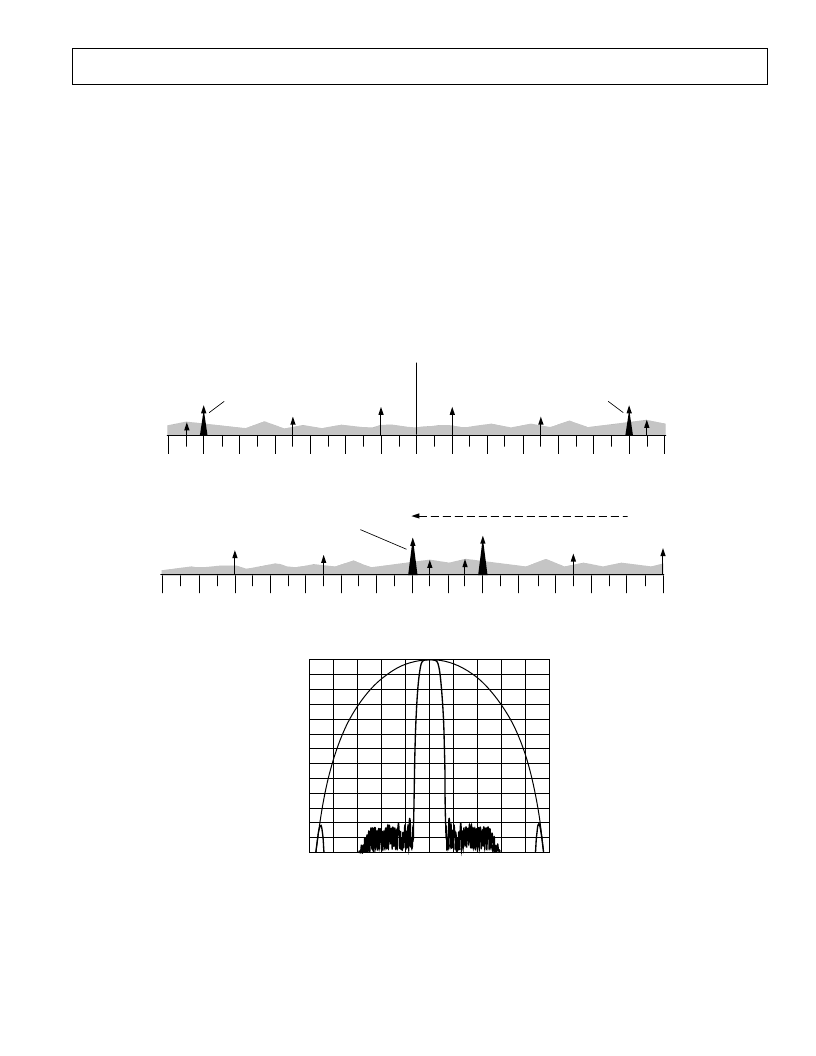

Figure 2 illustrates the basic function of the AD6620: to select

and filter a single channel from a wide input spectrum. The

frequency translator “tunes” the desired carrier to baseband.

CIC2 and CIC5 have fixed order responses; the RCF filter

provides the sharp transitions. More detail is provided in later

sections of the data sheet.

–f

S

/2

–3f

S

/8

–5f

S

/16

–f

S

/4

–3f

S

/16

–f

S

/8

–f

S

/16

DC

f

S

/16

f

S

/8

3f

S

/16

f

S

/4

5f

S

/16

f

S

/2

3f

S

/8

SIGNAL OF

INTEREST

SIGNAL OF INTEREST "IMAGE"

WIDEBAND INPUT SPECTRUM

(–f

samp/

2 TO f

samp/

2)

D'

C'

B'

A'

A

C

B

D

Figure 2a. Wideband Input Spectrum (e.g., 30 MHz from High Speed ADC)

–f

S

/2

–3f

S

/8

–5f

S

/16

–f

S

/4

–3f

S

/16

–f

S

/8

–f

S

/16

DC

f

S

/16

f

S

/8

3f

S

/16

f

S

/4

5f

S

/16

f

S

/2

3f

S

/8

AFTER FREQUENCY TRANSLATION

NCO "TUNES" SIGNAL TO BASEBAND

A

B

C

D

D'

C'

B'

A'

Figure 2b. Frequency Translation (e.g. Single 1 MHz Channel Tuned to Baseband)

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

–130

CIC2, CIC5, AND RCF

d

FREQUENCY

Figure 2c. Baseband Signal is Decimated and Filtered by CIC2, CIC5, RCF

相关PDF资料 |

PDF描述 |

|---|---|

| AD6620 | 65 MSPS Digital Receive Signal Processor(采样速率65MSPS的数字接收信号处理器) |

| AD6622AS | Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622PCB | Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622S | Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622 | Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6620S/PCB | 制造商:Analog Devices 功能描述:DUAL CHANNEL DECIMATING RECEIV 制造商:Analog Devices 功能描述:SGNL PROCESSOR 169CSPBGA - Bulk |

| AD6622 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622AS | 制造商:Analog Devices 功能描述:Transmit Signal Processor 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL 65 MSPS DIGITAL UPCONVERTER - Bulk |

| AD6622PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622S | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

发布紧急采购,3分钟左右您将得到回复。