- 您现在的位置:买卖IC网 > PDF目录373890 > AD6620S (Analog Devices, Inc.) 65 MSPS Digital Receive Signal Processor PDF资料下载

参数资料

| 型号: | AD6620S |

| 厂商: | Analog Devices, Inc. |

| 英文描述: | 65 MSPS Digital Receive Signal Processor |

| 中文描述: | 65 MSPS的数字接收信号处理器 |

| 文件页数: | 41/43页 |

| 文件大小: | 354K |

| 代理商: | AD6620S |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页

AD6620

–41–

REV. 0

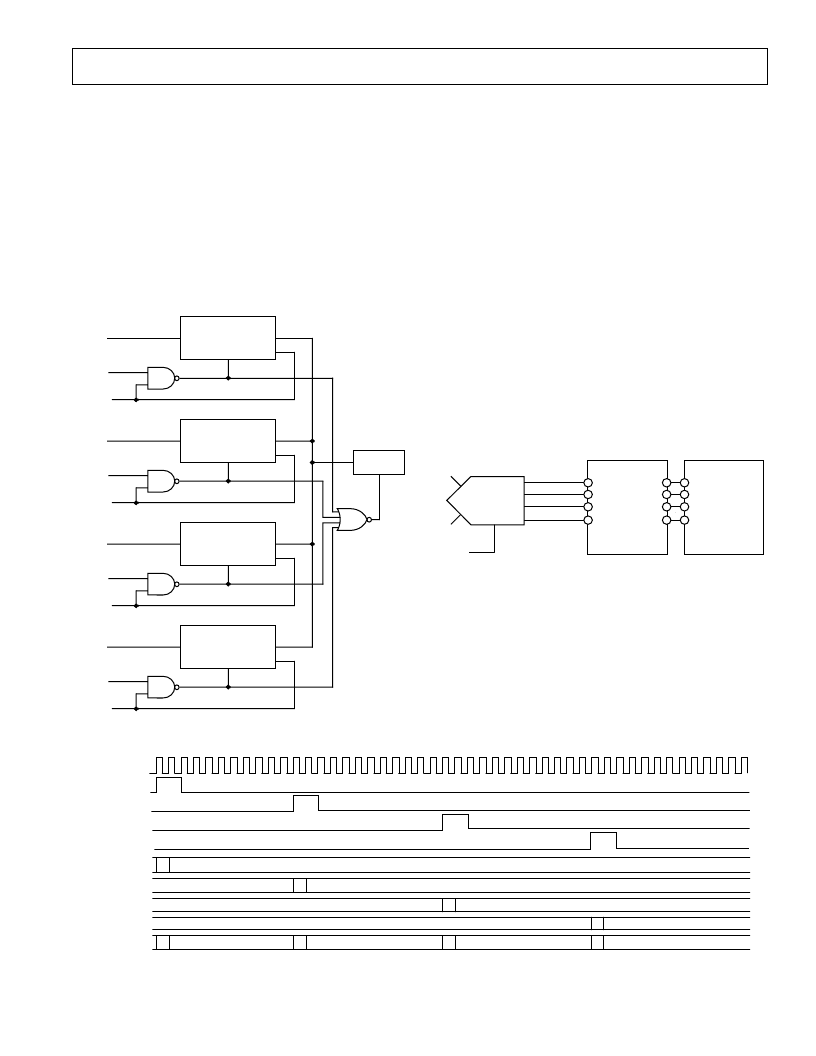

the outputs. Since the devices are operated in Single Channel

Real mode, this signal will be high for two clock cycles while

two pieces of data are written to the output. The output pairs

consist of I followed by Q. As each chip’s DV

OUT

cycles high, its

data should be connected to the output bus as shown below.

This effectively forms a MUX that sequentially cycles the out-

put of each of the AD6620s in the system to the output port.

The only remaining issue is retiming the data. Since each AD6620

clocks its data out in two clock cycles, there will be six cycles

where the data is idle. During this period, the last Q out will

remain valid until the next chip in the sequence generates its

DV

OUT

signal. This normally should pose no problem, but if it

does, the output data could easily go to a FIFO and be retimed

so that output data streams at a regular rate.

D

OUT1

CLOCK

DV

OUT1

OE

INPUT LATCHING

D

OUT1

CLOCK

DV

OUT2

OE

INPUT LATCHING

D

OUT1

CLOCK

DV

OUT3

OE

INPUT LATCHING

D

OUT1

CLOCK

DV

OUT4

OE

INPUT LATCHING

OUTPUT

LATCHING

Figure 59. Parallel Procession Output Selector

CLOCK

DV

OUT1

DV

OUT2

DV

OUT3

DV

OUT4

AD6620–1

AD6620–2

AD6620–3

AD6620–4

SELECTOR

OUTPUT

Q

I

Q

I

Q

I

Q

I

Q

I

Q

I

Q

I

Q

I

‘

Figure 60. Timing for Parallel Processing

In the Output Selector above each of the DV

OUT

lines is ANDed

with main clock. This allows the data out of each of the AD6620s

to be properly latched into the input latches. The DV

OUT

line is

also responsible for placing the latched outputs on the internal

bus at the proper time. This data is then latched in the output

latch using the internal ORed clocking signals.

The timing for these events is shown in Figure 60. As shown,

the system clock is run at the specified rate. Then the RCF

timing control state machine is responsible for generating the

appropriate sync pulses. When each AD6620 completes its SOP

computation, it generates the DV

OUT

pulses shown below. Con-

currently, each chip places its IQ data on the output pins of that

device. With this data, the output selector state machine com-

bines all of the data and places the data on the output bus.

Using the AD6620 in a Narrow Band System

A typical interconnection between the AD6600, AD6620 and a

General Purpose DSP. This is an example of an IF sampling

narrow-band system and offers many technical and cost advan-

tages over traditional solutions. In this example, the AD6620 is in

Diversity Channel Real Mode, with the AD6600 sampling a

diversity antenna on its B channel. The AD6620 performs float-

ing-point to fixed-point conversion, digital tuning, digital filter-

ing and decimation of the A/D output data.

MAIN

INPUT

DIVERSITY

INPUT

2

3

CLK

A/B OUT

3 RSSI BITS

11 DATA BITS

ENCODE

SCLK

SDI

SDO

SDFS

CLK

A/B

E[2...0]

IN[15...5]

AD6620

AD6600

SCLK

SDO

SDI

SDFS

DSP

Figure 61. Implementation of a Narrow Band Receiver

The 2

×

CLK on the AD6600 is used as the processing CLK of

the AD6620. The use of this faster clock allows the RCF filter to

process up to twice as many taps per sample. The increased

number of taps available helps to improve the filter characteris-

tics. In some applications an even faster processing clock may be

necessary to allow for improved digital filter performance. In this

case the A/B pin of the AD6620 must be toggled when each

channel input is to be sampled.

相关PDF资料 |

PDF描述 |

|---|---|

| AD6620 | 65 MSPS Digital Receive Signal Processor(采样速率65MSPS的数字接收信号处理器) |

| AD6622AS | Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622PCB | Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622S | Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622 | Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6620S/PCB | 制造商:Analog Devices 功能描述:DUAL CHANNEL DECIMATING RECEIV 制造商:Analog Devices 功能描述:SGNL PROCESSOR 169CSPBGA - Bulk |

| AD6622 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622AS | 制造商:Analog Devices 功能描述:Transmit Signal Processor 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL 65 MSPS DIGITAL UPCONVERTER - Bulk |

| AD6622PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622S | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

发布紧急采购,3分钟左右您将得到回复。