参数资料

| 型号: | AD73311ARSZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/36页 |

| 文件大小: | 0K |

| 描述: | IC ANALOG FRONT END 20-SSOP |

| 标准包装: | 66 |

| 位数: | 16 |

| 通道数: | 2 |

| 功率(瓦特): | 50mW |

| 电压 - 电源,模拟: | 3V |

| 电压 - 电源,数字: | 3V |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 管件 |

| 产品目录页面: | 799 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD73311

–23–

REV. B

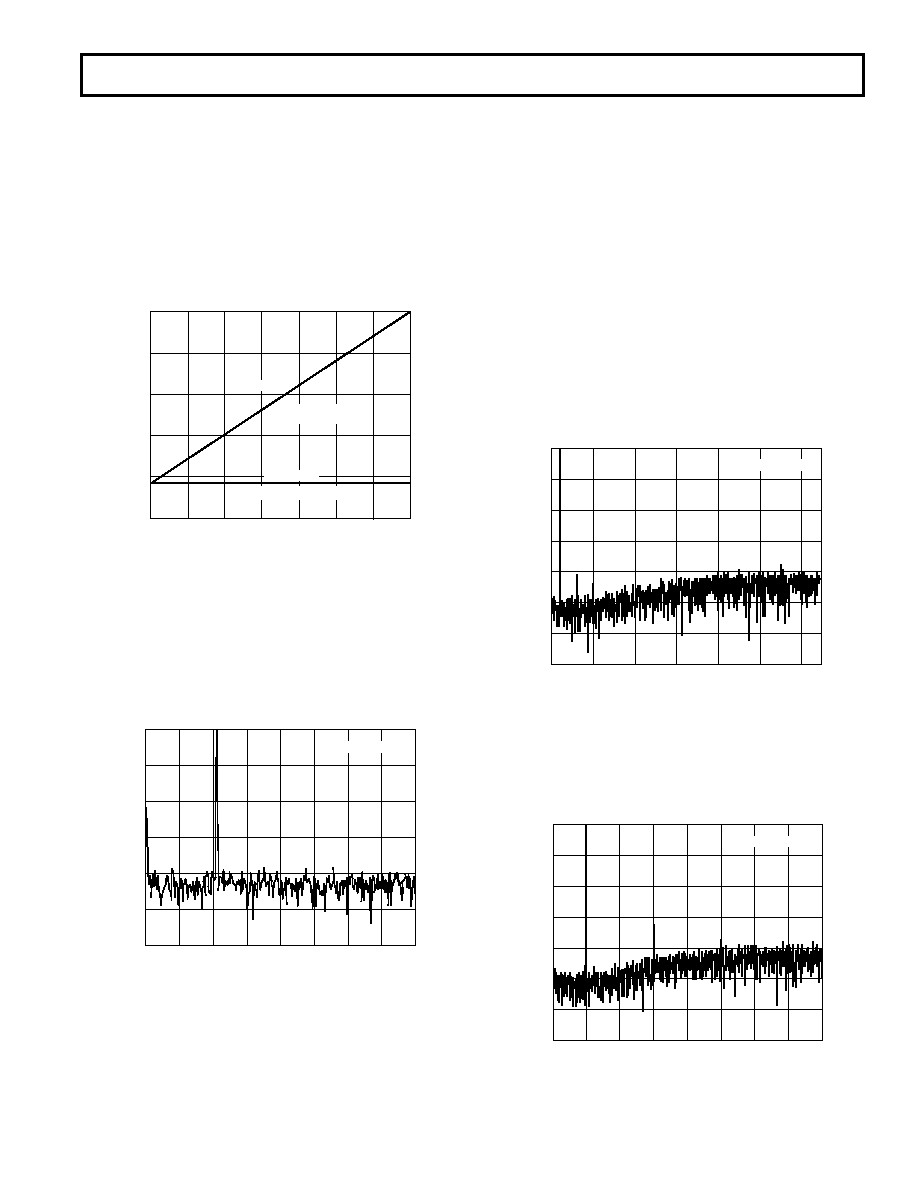

In order to produce a direct sampling rate of 8 kHz, it is

necessary to reduce the external master clock to 8.192 MHz and

to set the master clock divider to a ratio of 4, which results in a

sample rate of 8 kHz. In this case, the response of the Sinc

3

decimation filter may affect the response in the voice BW as its

first null occurs at 8 kHz. In Figure 17, Trace A shows how the

SNR remains approximately constant up to FS/2 regardless of

the sample rate FS; Trace B shows that the SNR achievable in

the voice BW is proportional to the sampling rate FS. These two

traces intersect at an FS of 8 kHz which is the point where FS/2

equals the voice BW.

SAMPLING FREQUENCY (DMCLK/256) – kHz

816

24

32

40

48

56

64

80

70

S/(N+D)

–

dB

65

55

75

60

SNR IN VOICEBAND

(300Hz–3400Hz)

SNR IN BAND UP TO FS/2

TRACE B

TRACE A

Figure 17. SNR vs. Sampling Frequency

If the input signal is externally band-limited, it is possible to

achieve the 8 kHz sampling rate directly from the 64 kHz

sample rate by decimating the sampled data in the DSP. This

technique will alias the band between 8 kHz and 64 kHz into

the 8 kHz band, therefore it is necessary to have good quality

external band-limiting on the input signal. Figure 18 shows the

spectral response of using this decimation technique for sample

rate reduction.

FREQUENCY – kHz

0

–120

0

4.0

0.5

dB

1.0

1.5

2.0

2.5

3.0

3.5

–20

–60

–80

–100

–40

S/N+D = 59.545

Figure 18. FFT (ADC 8 kHz Subsampled)

Encoder Group Delay

The AD73311 implementation offers a very low level of group

delay, which is given by the following relationship:

Group Delay (Decimator) = Order

× ((M–1)/2) × Tdec

where:

Order is the order of the decimator (= 3),

M is the decimation factor (= 32) and

Tdec is the decimation sample interval (= 1/2.048e6)

=> Group Delay (Decimator) = 3

× (32–1)/2 × (1/2.048e6)

= 22.7

s

If final filtering is implemented in the DSP, the final filter’s

group delay must be taken into account when calculating overall

group delay.

Decoder Section

The decoder section updates (samples) at the same rate as the

encoder section, MCLK/256, which gives a 64 kHz rate from an

external MCLK of 16.384 MHz. Figure 19 shows the spectral

response of the decoder section sampling at 64 kHz. Again, its

sigma-delta modulator shapes the noise so it is reduced in the

voice bandwidth dc–4 kHz. For improved voiceband SNR, the

user can implement an initial anti-imaging filter, preceded by

8 kHz to 64 kHz interpolation, in the DSP.

FREQUENCY – kHz

0

–140

032

5

dB

10

15

20

25

30

–20

–60

–80

–100

–120

–40

S/N+D = 58.454842

Figure 19. FFT (DAC 64 kHz Sampling)

As is the case with the encoder section, voiceband SNR is re-

duced if the DMCLK rate is reduced as shown by the example

of 16 kHz sampling in Figure 20. This is due to the noise-shap-

ing of the sigma-delta modulator being compressed into a

smaller bandwidth, which increases the noise in the voice BW.

FREQUENCY – kHz

0

–140

08

12

3

4

5

67

–20

–60

–80

–100

–120

–40

dB

S/N+D = 57.441659

Figure 20. FFT (DAC 16 kHz Sampling)

相关PDF资料 |

PDF描述 |

|---|---|

| AD73322LARUZ-REEL | IC PROCESSOR FRONTEND DL 28TSSOP |

| AD73322LYRZ | IC ANALOG FRONT END DUAL 28-SOIC |

| AD73360ARZ | IC PROCESSOR FRONTEND 6CH 28SOIC |

| AD7352YRUZ-500RL7 | IC ADC DUAL 12BIT 3MSPS 16TSSOP |

| AD7356YRUZ-500RL7 | IC ADC DUAL 12BIT 5MSPS 16TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD73311ARSZ-REEL | 功能描述:IC ANALOG FRONT END 20-SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73311ARZ | 功能描述:IC PROCESSOR FRONT END LP 20SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73311ARZ-REEL | 功能描述:IC PROCESSOR FRONT END LP 20SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73311L | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost, Low Power CMOS General Purpose Analog Front End |

| AD73311LAR | 制造商:Analog Devices 功能描述:Audio Codec 1ADC / 1DAC 16-Bit 20-Pin SOIC W 制造商:Rochester Electronics LLC 功能描述:SINGLE-CHANNEL AFE I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。