参数资料

| 型号: | AD73311ARSZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 17/36页 |

| 文件大小: | 0K |

| 描述: | IC ANALOG FRONT END 20-SSOP |

| 标准包装: | 66 |

| 位数: | 16 |

| 通道数: | 2 |

| 功率(瓦特): | 50mW |

| 电压 - 电源,模拟: | 3V |

| 电压 - 电源,数字: | 3V |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 管件 |

| 产品目录页面: | 799 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD73311

–24–

REV. B

It is also possible to subsample the DAC—update at a lower rate

than the sampling rate—to reduce the overhead on the DSP.

This, however, results in imaging of the subsampled bandwidth

into the normal bandwidth, which implies that higher perfor-

mance external anti-imaging filtering must be used to eliminate

the images.

The interpolator input also provides a minimum group delay

realization in situations where that is critical. Further reduction

in group delay is possible by accessing the digital sigma-delta

input at the expense of lower attenuation of images due to any

repetition of input samples. Figure 21 shows the spectral

response of the decoder being sampled at 64 kHz with its inter-

polator bypassed.

FREQUENCY – kHz

0

–140

032

510

15

20

25

30

–20

–60

–80

–100

–120

–40

dB

S/N+D = 58.557732

Figure 21. FFT (DAC 64 kHz Sampling—Interpolator

Bypassed)

Decoder Group Delay

The interpolator roll-off is mainly due to its sync-cubed function

characteristic, which has an inherent group delay given by the

equation.

Group Delay (Interpolator) = Order

× (L – 1)/2) × Tint

where:

Order is the interpolator order (= 3),

L is the interpolation factor (= 32) and

Tint is the interpolation sample interval

(= 1/2.048e6)

=> Group Delay (Interpolator)

= 3*(32-1)/2*(1/2.048e6)

= 22.7

s

The analog section has a group delay of approximately 25

s.

DESIGN CONSIDERATIONS

Analog Input

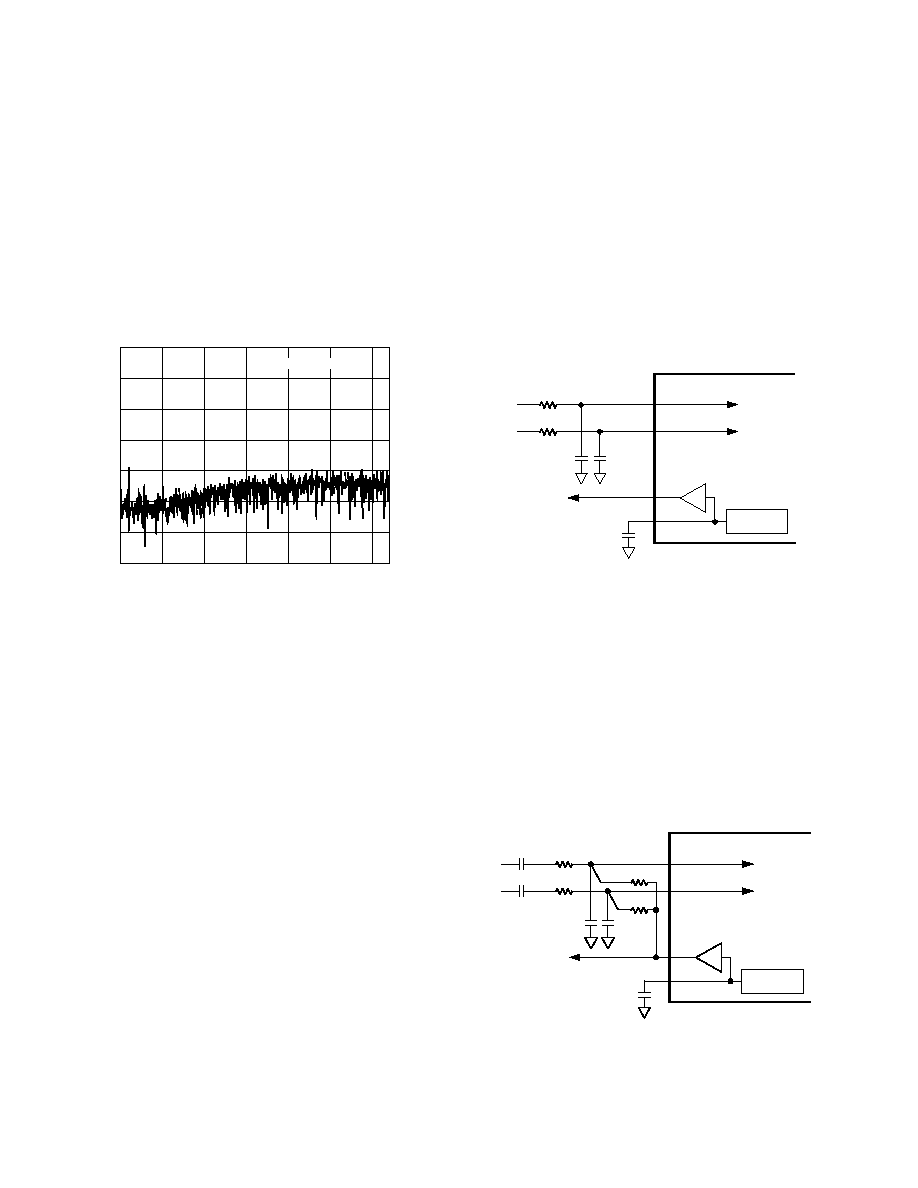

The analog input signal to the codec can be dc coupled, pro-

vided that the dc bias level of the input signal is the same as the

internal reference level (REFOUT). Figure 22 shows the recom-

mended differential input circuit for the AD73311’s analog

input pins (VIN). The circuit of Figure 22 implements first-

order low-pass filters with a 3 dB point at 34 kHz; these are the

only filters that must be implemented external to the AD73311

to prevent aliasing of the sampled signal. Since the codec’s ADC

uses a highly oversampled approach that transfers the bulk of

the antialiasing filtering into the digital domain, the off-chip

antialiasing filter need only be of a low order. It is recommended

that for optimum performance that the capacitors used for the

antialiasing filter be of high quality dielectric (NPO).

REFCAP

VOLTAGE

REFERENCE

0.1 F

REFOUT

TO INPUT BIAS

CIRCUITRY

100

VIN

0.047 F

VINN

VINP

AD73311

Figure 22. Example Circuit for Differential Input

(DC Coupling)

The AD73311’s on-chip 38 dB preamplifier can be enabled when

there is not enough gain in the input circuit; the preamplifier is

configured by bits IGS0–2 of CRD. The total gain must be

configured to ensure that a full-scale input signal produces a

signal level at the input to the sigma-delta modulator of the

ADC that does not exceed the maximum input range.

The dc biasing of the analog input signal is accomplished with

an on-chip voltage reference. If the input signal is not biased at

the internal reference level (via REFOUT), then it must be ac-

coupled with external coupling capacitors. CIN should be 0.1

F

or larger. The dc biasing of the input can then be accomplished

using resistors to REFOUT as in Figure 23.

REFCAP

VOLTAGE

REFERENCE

0.1 F

REFOUT

TO INPUT BIAS

CIRCUITRY

100

VIN

CIN

0.047 F

VINN

VINP

10k

AD73311

Figure 23. Example Circuit for Differential Input

(AC Coupling)

相关PDF资料 |

PDF描述 |

|---|---|

| AD73322LARUZ-REEL | IC PROCESSOR FRONTEND DL 28TSSOP |

| AD73322LYRZ | IC ANALOG FRONT END DUAL 28-SOIC |

| AD73360ARZ | IC PROCESSOR FRONTEND 6CH 28SOIC |

| AD7352YRUZ-500RL7 | IC ADC DUAL 12BIT 3MSPS 16TSSOP |

| AD7356YRUZ-500RL7 | IC ADC DUAL 12BIT 5MSPS 16TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD73311ARSZ-REEL | 功能描述:IC ANALOG FRONT END 20-SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73311ARZ | 功能描述:IC PROCESSOR FRONT END LP 20SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73311ARZ-REEL | 功能描述:IC PROCESSOR FRONT END LP 20SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73311L | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost, Low Power CMOS General Purpose Analog Front End |

| AD73311LAR | 制造商:Analog Devices 功能描述:Audio Codec 1ADC / 1DAC 16-Bit 20-Pin SOIC W 制造商:Rochester Electronics LLC 功能描述:SINGLE-CHANNEL AFE I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。