- 您现在的位置:买卖IC网 > PDF目录10744 > AD7730BRU-REEL7 (Analog Devices Inc)IC ADC TRANSDUCER BRIDGE 24TSSOP PDF资料下载

参数资料

| 型号: | AD7730BRU-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 27/53页 |

| 文件大小: | 0K |

| 描述: | IC ADC TRANSDUCER BRIDGE 24TSSOP |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 通道数: | 1 |

| 功率(瓦特): | 125mW |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 2.7 V ~ 5.25 V |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 24-TSSOP |

| 包装: | 带卷 (TR) |

| 配用: | EVAL-AD7730LEBZ-ND - BOARD EVALUATION FOR AD7730 EVAL-AD7730EBZ-ND - BOARD EVAL FOR AD7730 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页

AD7730/AD7730L

–33–

AD7730

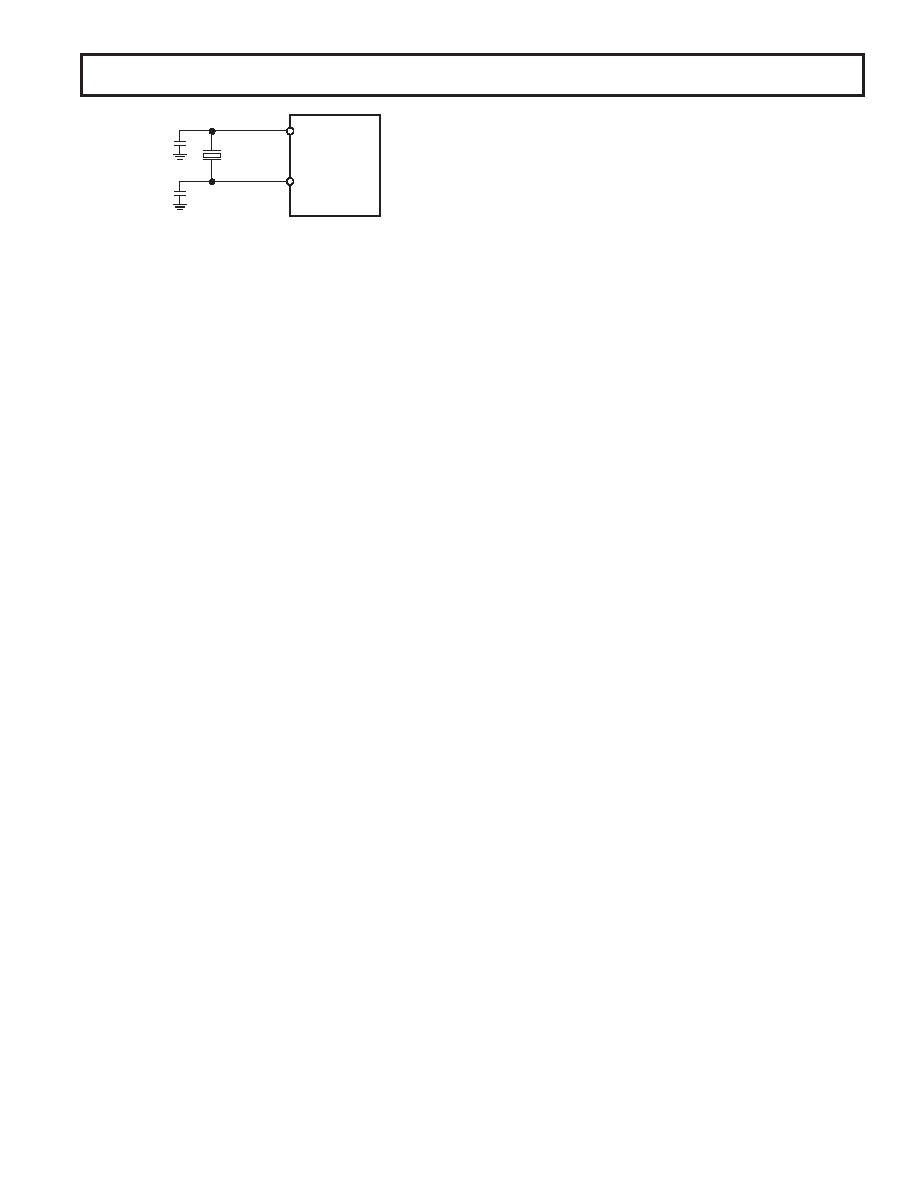

CRYSTAL OR

CERAMIC

RESONATOR

C1

C2

MCLK IN

MCLK OUT

Figure 17. Crystal/Resonator Connections

The on-chip oscillator circuit also has a start-up time associated

with it before it has attained its correct frequency and correct

voltage levels. The typical start-up time for the circuit is 6 ms,

with a DVDD of +5 V and 8 ms with a DVDD of +3 V.

The AD7730’s master clock appears on the MCLK OUT pin of

the device. The maximum recommended load on this pin is one

CMOS load. When using a crystal or ceramic resonator to gen-

erate the AD7730’s clock, it may be desirable to then use this

clock as the clock source for the system. In this case, it is recom-

mended that the MCLK OUT signal is buffered with a CMOS

buffer before being applied to the rest of the circuit.

System Synchronization

The

SYNC input allows the user to reset the modulator and

digital filter without affecting any of the setup conditions on the

part. This allows the user to start gathering samples of the ana-

log input from a known point in time, i.e., the rising edge of

SYNC.

If multiple AD7730s are operated from a common master clock,

they can be synchronized to update their output registers simul-

taneously. A falling edge on the

SYNC input resets the digital

filter and analog modulator and places the AD7730 into a con-

sistent, known state. While the

SYNC input is low, the AD7730

will be maintained in this state. On the rising edge of

SYNC,

the modulator and filter are taken out of this reset state and on

the next clock edge the part starts to gather input samples again.

In a system using multiple AD7730s, a common signal to their

SYNC inputs will synchronize their operation. This would nor-

mally be done after each AD7730 has performed its own cali-

bration or has had calibration coefficients loaded to it. The

output updates will then be synchronized with the maximum

possible difference between the output updates of the individual

AD7730s being one MCLK IN cycle.

Single-Shot Conversions

The

SYNC input can also be used as a start convert command

allowing the AD7730 to be operated in a conventional converter

fashion. In this mode, the rising edge of

SYNC starts conversion

and the falling edge of

RDY indicates when conversion is com-

plete. The disadvantage of this scheme is that the settling time

of the filter has to be taken into account for every data register

update.

Writing 0, 1, 0 to the MD2, MD1, MD0 bits of the Mode regis-

ter has the same effect. This initiates a single conversion on the

AD7730 with the part returning to idle mode at the end of

conversion. Once again, the full settling-time of the filter has to

elapse before the Data Register is updated.

Reset Input

The

RESET input on the AD7730 resets all the logic, the digital

filter and the analog modulator while all on-chip registers are

reset to their default state.

RDY is driven high and the AD7730

ignores all communications to any of its registers while the

RESET input is low. When the RESET input returns high, the

AD7730 starts to process data and

RDY will return low after

the filter has settled indicating a valid new word in the data

register. However, the AD7730 operates with its default setup

conditions after a

RESET and it is generally necessary to set up all

registers and carry out a calibration after a

RESET command.

The AD7730’s on-chip oscillator circuit continues to function

even when the

RESET input is low. The master clock signal

continues to be available on the MCLK OUT pin. Therefore, in

applications where the system clock is provided by the AD7730’s

clock, the AD7730 produces an uninterrupted master clock

during

RESET commands.

Standby Mode

The

STANDBY input on the AD7730 allows the user to place

the part in a power-down mode when it is not required to pro-

vide conversion results. The part can also be placed in its

standby mode by writing 0, 1, 1 to the MD2, MD1, MD0 bits

of the Mode Register. The AD7730 retains the contents of all its

on-chip registers (including the Data Register) while in standby

mode. Data can still be read from the part in Standby Mode.

The STBY bit of the Status Register indicates whether the part

is in standby or normal operating mode. When the

STANDBY

pin is taken high, the part returns to operating as it had been

prior to the

STANDBY pin going low.

The

STANDBY input (or 0, 1, 1 in the MD2, MD1, MD0 bits)

does not affect the digital interface. It does, however, set the

RDY bit and pin high and also sets the STDY bit high. When

STANDBY goes high again, RDY and STDY remain high until

set low by a conversion or calibration.

Placing the part in standby mode, reduces the total current to

10

μA typical when the part is operated from an external master

clock provided this master clock is stopped. If the external clock

continues to run in standby mode, the standby current increases

to 400

μA typical. If a crystal or ceramic resonator is used as the

clock source, then the total current in standby mode is 400

μA

typical. This is because the on-chip oscillator circuit continues

to run when the part is in its standby mode. This is important in

applications where the system clock is provided by the AD7730’s

clock, so that the AD7730 produces an uninterrupted master

clock even when it is in its standby mode.

Digital Outputs

The AD7730 has two digital output pins, D0 and D1. When the

DEN bit of the Mode Register is set to 1, these digital outputs

assume the logic status of bits D0 and D1 of the Mode Register.

It gives the user access to two digital port pins which can be

programmed over the normal serial interface of the AD7730.

The two outputs obtain their supply voltage from AVDD,

thus the outputs operate to 5 V levels even in cases where

DVDD = +3 V.

REV. B

相关PDF资料 |

PDF描述 |

|---|---|

| AD7730BRU-REEL | IC ADC TRANSDUCER BRIDGE 24TSSOP |

| AD7730BR-REEL | IC ADC TRANSDUCER BRIDGE 24-SOIC |

| AD7730LBR-REEL7 | IC ADC TRANSDUCER BRIDGE 24SOIC |

| XRD9824ACD-F | IC 14B CCD/CIS SIG PROC 20SOIC |

| MAX933CSA+ | IC COMPARATOR W/REF 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7730BRUZ | 功能描述:IC ADC TRANSDUCER BRIDGE 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRUZ-REEL | 功能描述:IC ADC BRIDGE TRANSDUCER 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRUZ-REEL7 | 功能描述:IC ADC BRIDGE TRANSDUCER 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRZ | 功能描述:IC ADC BRIDGE TRANSDUCER 24-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRZ | 制造商:Analog Devices 功能描述:IC, ADC, 24BIT, 1.2KSPS, SOIC-24 |

发布紧急采购,3分钟左右您将得到回复。