- 您现在的位置:买卖IC网 > PDF目录10744 > AD7730BRU-REEL7 (Analog Devices Inc)IC ADC TRANSDUCER BRIDGE 24TSSOP PDF资料下载

参数资料

| 型号: | AD7730BRU-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 43/53页 |

| 文件大小: | 0K |

| 描述: | IC ADC TRANSDUCER BRIDGE 24TSSOP |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 通道数: | 1 |

| 功率(瓦特): | 125mW |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 2.7 V ~ 5.25 V |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 24-TSSOP |

| 包装: | 带卷 (TR) |

| 配用: | EVAL-AD7730LEBZ-ND - BOARD EVALUATION FOR AD7730 EVAL-AD7730EBZ-ND - BOARD EVAL FOR AD7730 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页

AD7730/AD7730L

–48–

OUTPUT NOISE AND RESOLUTION SPECIFICATION

The AD7730L can be programmed to operate in either chop mode or nonchop mode. The chop mode can be enabled in ac-excited

or dc-excited applications; it is optional in dc-excited applications, but chop mode must be enabled in ac-excited applications. These

options are discussed in more detail in earlier sections. The chop mode has the advantage of lower drift numbers and better noise

immunity, but the noise is approximately 20% higher for a given –3 dB frequency and output data rate. It is envisaged that the major-

ity of weigh-scale users of the AD7730L will operate the part in chop mode to avail themselves of the excellent drift performance and

noise immunity when chopping is enabled. The following tables outline the noise performance of the part in both chop and nonchop

modes over all input ranges for a selection of output rates.

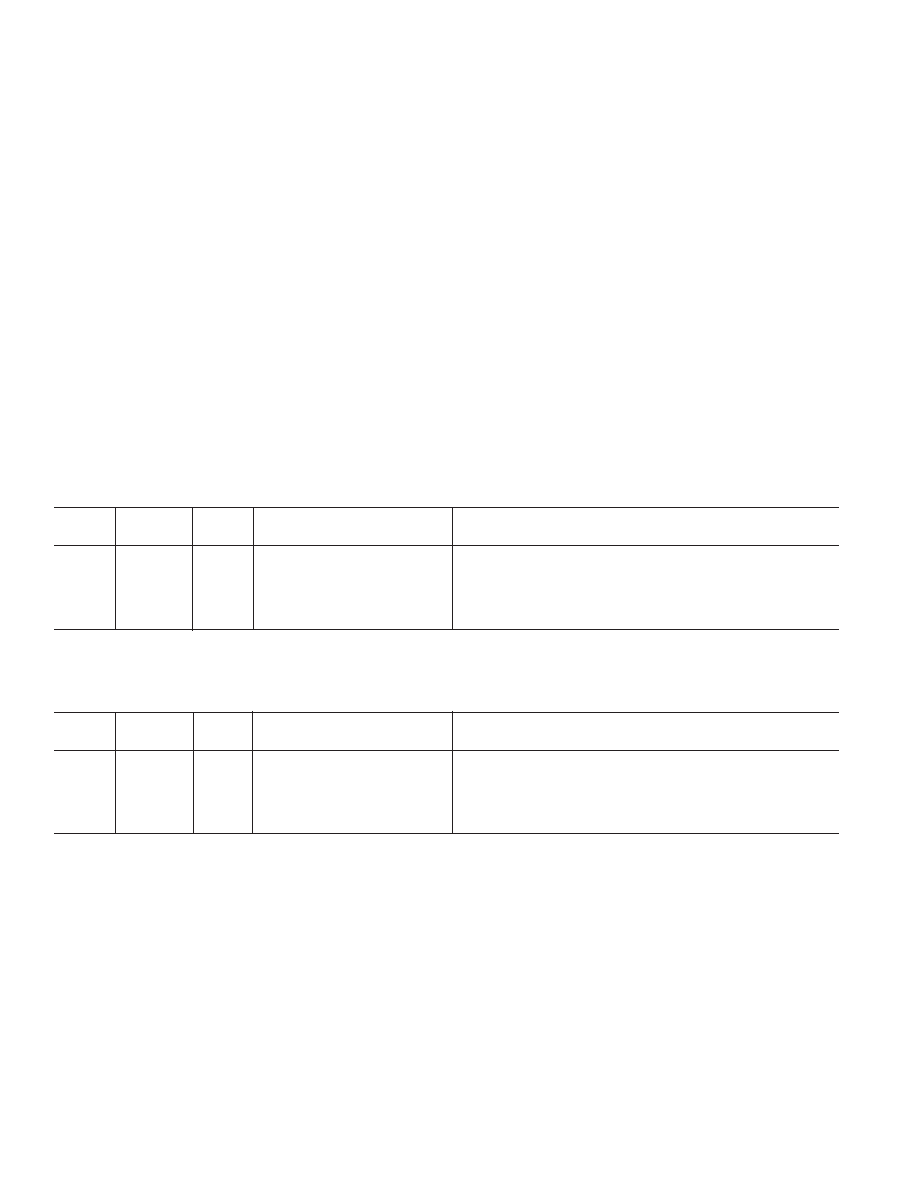

Output Noise (CHP = 1)

This mode is the primary mode of operation of the device. Table XXI shows the output rms noise for some typical output update

rates and –3 dB frequencies for the AD7730 when used in chopping mode (CHP of Filter Register = 1) with a master clock

frequency of 2.4576 MHz. These numbers are typical and are generated at a differential analog input voltage of 0 V. The output

update rate is selected via the SF0 to SF11 bits of the Filter Register. Table XXII, meanwhile, shows the output peak-to-peak resolu-

tion in counts for the same output update rates. The numbers in brackets are the effective peak-to-peak resolution in bits (rounded to

the nearest 0.5 LSB). It is important to note that the numbers in Table XXII represent the resolution for which there will be no code

flicker within a six-sigma limit. They are not calculated based on rms noise, but on peak-to-peak noise.

The numbers are generated for the bipolar input ranges. When the part is operated in unipolar mode, the output noise will be the

same as the equivalent bipolar input range. As a result, the numbers in Table XXI will remain the same for unipolar ranges while the

numbers in Table II will change. To calculate the numbers for Table XXII for unipolar input ranges simply divide the peak-to-peak

resolution number in counts by two or subtract one from the peak-to-peak resolution number in bits.

Table XXI. Output Noise vs. Input Range and Update Rate (CHP = 1)

Typical Output RMS Noise in nV

Output

–3 dB

SF

Settling Time

Input Range

Data Rate Frequency

Word

Normal Mode

Fast Mode

= 80 mV

= 40 mV

= 20 mV

= 10 mV

25 Hz

0.98 Hz

2048

920 ms

120 ms

245

140

105

70

50 Hz

1.97 Hz

1024

460 ms

60 ms

340

220

160

100

75 Hz

2.96 Hz

683

306 ms

40 ms

420

270

170

110

100 Hz*

3.95 Hz

512

230 ms

30 ms

500

290

180

130

200 Hz

7.9 Hz

256

115 ms

15 ms

650

490

280

165

*Power-On Default

Table XXII. Peak-to-Peak Resolution vs. Input Range and Update Rate (CHP = 1)

Peak-to-Peak Resolution in Counts (Bits)

Output

–3 dB

SF

Settling Time

Input Range

Data Rate Frequency

Word

Normal Mode

Fast Mode

= 80 mV

= 40 mV

= 20 mV

= 10 mV

25 Hz

0.98 Hz

2048

920 ms

120 ms

110k (17)

94k (16.5)

64k (16)

46k (15.5)

50 Hz

1.97 Hz

1024

460 ms

60 ms

80k (16.5)

60k (16)

42k (15.5)

33k (15)

75 Hz

2.96 Hz

683

306 ms

40 ms

62k (16)

50k (15.5)

39k (15)

31k (15)

100 Hz*

3.95 Hz

512

230 ms

30 ms

53k (15.5)

46k (15.5)

36k (15)

25k (14.5)

200 Hz

7.9 Hz

256

115 ms

15 ms

44k (15.5)

27k (15)

24k (14.5)

20k (14.5)

*Power-On Default

Output Noise (CHP = 0)

Table XXIII shows the output rms noise for some typical output update rates and –3 dB frequencies for the AD7730L when used in

nonchopping mode (CHP of Filter Register = 0) with a master clock frequency of 2.4576 MHz. These numbers are typical and are

generated at a differential analog input voltage of 0 V. The output update rate is selected via the SF0 to SF11 bits of the Filter Regis-

ter. Table XXIV, meanwhile, shows the output peak-to-peak resolution in counts for the same output update rates. The numbers in

brackets are the effective peak-to-peak resolution in bits (rounded to the nearest 0.5 LSB). It is important to note that the numbers in

Table XXIV represent the resolution for which there will be no code flicker within a six-sigma limit. They are not calculated based on

rms noise, but on peak-to-peak noise.

The numbers are generated for the bipolar input ranges. When the part is operated in unipolar mode, the output noise will be the

same as the equivalent bipolar input range. As a result, the numbers in Table XXIII will remain the same for unipolar ranges while

the numbers in Table XXIV will change. To calculate the number for Table XXIV for unipolar input ranges simply divide the peak-

to-peak resolution number in counts by two or subtract one from the peak-to-peak resolution number in bits.

REV. B

相关PDF资料 |

PDF描述 |

|---|---|

| AD7730BRU-REEL | IC ADC TRANSDUCER BRIDGE 24TSSOP |

| AD7730BR-REEL | IC ADC TRANSDUCER BRIDGE 24-SOIC |

| AD7730LBR-REEL7 | IC ADC TRANSDUCER BRIDGE 24SOIC |

| XRD9824ACD-F | IC 14B CCD/CIS SIG PROC 20SOIC |

| MAX933CSA+ | IC COMPARATOR W/REF 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7730BRUZ | 功能描述:IC ADC TRANSDUCER BRIDGE 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRUZ-REEL | 功能描述:IC ADC BRIDGE TRANSDUCER 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRUZ-REEL7 | 功能描述:IC ADC BRIDGE TRANSDUCER 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRZ | 功能描述:IC ADC BRIDGE TRANSDUCER 24-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRZ | 制造商:Analog Devices 功能描述:IC, ADC, 24BIT, 1.2KSPS, SOIC-24 |

发布紧急采购,3分钟左右您将得到回复。