- 您现在的位置:买卖IC网 > PDF目录10744 > AD7730BRU-REEL7 (Analog Devices Inc)IC ADC TRANSDUCER BRIDGE 24TSSOP PDF资料下载

参数资料

| 型号: | AD7730BRU-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 51/53页 |

| 文件大小: | 0K |

| 描述: | IC ADC TRANSDUCER BRIDGE 24TSSOP |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 通道数: | 1 |

| 功率(瓦特): | 125mW |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 2.7 V ~ 5.25 V |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 24-TSSOP |

| 包装: | 带卷 (TR) |

| 配用: | EVAL-AD7730LEBZ-ND - BOARD EVALUATION FOR AD7730 EVAL-AD7730EBZ-ND - BOARD EVAL FOR AD7730 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页当前第51页第52页第53页

AD7730/AD7730L

–7–

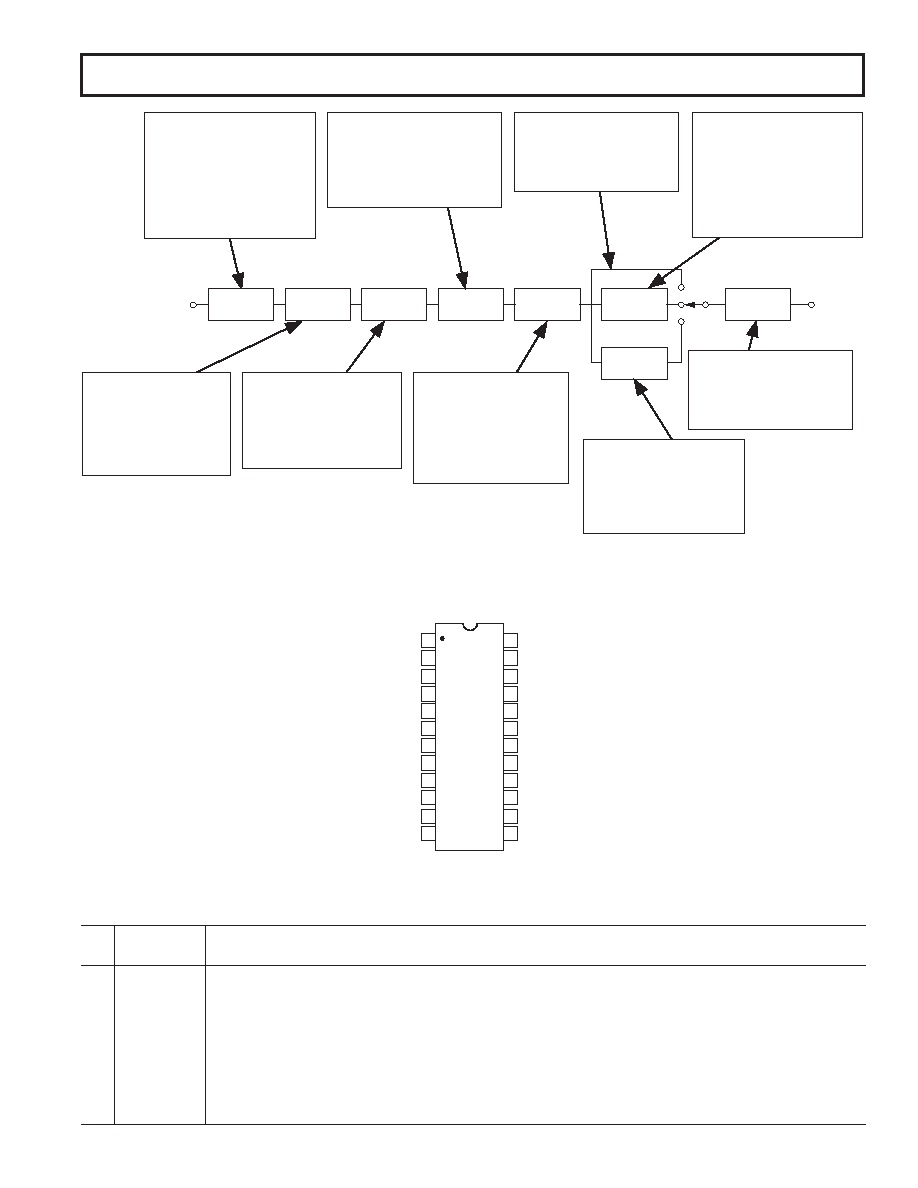

Figure 3. Signal Processing Chain

PIN CONFIGURATION

PIN FUNCTION DESCRIPTIONS

Pin

No.

Mnemonic

Function

1

SCLK

Serial Clock. Schmitt-Triggered Logic Input. An external serial clock is applied to this input to transfer serial

data to or from the AD7730. This serial clock can be a continuous clock with all data transmitted in a con-

tinuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted

to or from the AD7730 in smaller batches of data.

2

MCLK IN

Master Clock signal for the device. This can be provided in the form of a crystal/resonator or external clock. A

crystal/resonator can be tied across the MCLK IN and MCLK OUT pins. Alternatively, the MCLK IN pin

can be driven with a CMOS-compatible clock and MCLK OUT left unconnected. The AD7730 is specified

with a clock input frequency of 4.9152 MHz while the AD7730L is specified with a clock input frequency of

2.4576 MHz.

SCLK

MCLK IN

DGND

DVDD

SYNC

VBIAS

RDY

CS

MCLK OUT

POL

DIN

DOUT

AGND

AVDD

ACX

AIN1(+)

STANDBY

14

1

2

24

23

5

6

7

20

19

18

3

4

22

21

8

17

9

16

10

15

11

TOP VIEW

(Not to Scale)

12

13

AD7730

RESET

REF IN(–)

REF IN(+)

AIN1(–)

AIN2(+)/D1

AIN2(–)/D0

ACX

PGA +

SIGMA-DELTA

MODULATOR

SINC3 FILTER

CHOP

22-TAP

FIR FILTER

FASTSTEP

FILTER

CHOP

INPUT CHOPPING

THE ANALOG INPUT TO THE PART CAN BE

CHOPPED. IN CHOPPING MODE, WITH

AC EXCITATION DISABLED, THE INPUT

CHOPPING IS INTERNALTO THE DEVICE. IN

CHOPPING MODE, WITH AC EXCITATION

ENABLED, THE CHOPPING IS ASSUMED

TO BE PERFORMED EXTERNAL TO THE PART

AND NO INTERNAL INPUT CHOPPING IS

PERFORMED. THE INPUT CHOPPING CAN

BE DISABLED, IF DESIRED.

SEE PAGE 26

ANALOG

INPUT

DIGITAL

OUTPUT

SINC3 FILTER

THE FIRST STAGE OF THE DIGITAL FILTERING

ON THE PART IS THE SINC3 FILTER. THE

OUTPUT UPDATE RATE AND BANDWIDTH

OF THIS FILTER CAN BE PROGRAMMED. IN

SKIP MODE, THE SINC3 FILTER IS THE

ONLY FILTERING PERFORMED ON THE PART.

SEE PAGE 26

BUFFER

SKIP MODE

IN SKIP MODE, THERE IS NO SECOND

STAGE OF FILTERING ON THE PART. THE

SINC3 FILTER IS THE ONLY FILTERING

PERFORMED ON THE PART.

SEE PAGE 29

SKIP

OUTPUT

SCALING

22-TAP FIR FILTER

IN NORMAL OPERATING MODE, THE

SECOND STAGE OF THE DIGITAL FILTERING

ON THE PART IS A FIXED 22-TAP FIR

FILTER. IN SKIP MODE, THIS FIR FILTER IS

BYPASSED. WHEN FASTSTEP MODE IS

ENABLED AND A STEP INPUT IS

DETECTED, THE SECOND STAGE FILTERING

IS PERFORMED BY THE FILTER

UNTIL THE OUTPUT OF THIS FILTER

HAS FULLY SETTLED.

SEE PAGE 27

OUTPUT SCALING

THE OUTPUT WORD FROM THE DIGITAL

FILTER IS SCALED BY THE CALIBRATION

COEFFICIENTS BEFORE BEING PROVIDED

AS THE CONVERSION RESULT.

SEE PAGE 29

FASTSTEP FILTER

WHEN FASTSTEP MODE IS ENABLED

AND A STEP CHANGE ON THE INPUT

HAS BEEN DETECTED, THE SECOND

STAGE FILTERING IS PERFORMED BY THE

FASTSTEP FILTER UNTIL THE FIR

FILTER HAS FULLY SETTLED.

SEE PAGE 29

OUTPUT CHOPPING

THE OUTPUT OF THE FIRST STAGE

OF FILTERING ON THE PART CAN

BE CHOPPED. IN CHOPPING MODE,

REGARDLESS OF WHETHER AC

EXCITATION IS ENABLED OR DISABLED,

THE OUTPUT CHOPPING IS

PERFORMED. THE CHOPPING CAN

BE DISABLED, IF DESIRED.

SEE PAGE 26

PGA + SIGMA-DELTA MODULATOR

THE PROGRAMMABLE GAIN CAPABILITY

OF THE PART IS INCORPORATED

AROUND THE SIGMA-DELTA MODULATOR.

THE MODULATOR PROVIDES A HIGH-

FREQUENCY 1-BIT DATA STREAM

TO THE DIGITAL FILTER.

SEE PAGE 26

BUFFER

THE INPUT SIGNAL IS BUFFERED

ON-CHIP BEFORE BEING APPLIED TO

THE SAMPLING CAPACITOR OF THE

SIGMA-DELTA MODULATOR. THIS

ISOLATES THE SAMPLING CAPACITOR

CHARGING CURRENTS FROM THE

ANALOG INPUT PINS.

SEE PAGE 24

REV. B

相关PDF资料 |

PDF描述 |

|---|---|

| AD7730BRU-REEL | IC ADC TRANSDUCER BRIDGE 24TSSOP |

| AD7730BR-REEL | IC ADC TRANSDUCER BRIDGE 24-SOIC |

| AD7730LBR-REEL7 | IC ADC TRANSDUCER BRIDGE 24SOIC |

| XRD9824ACD-F | IC 14B CCD/CIS SIG PROC 20SOIC |

| MAX933CSA+ | IC COMPARATOR W/REF 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7730BRUZ | 功能描述:IC ADC TRANSDUCER BRIDGE 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRUZ-REEL | 功能描述:IC ADC BRIDGE TRANSDUCER 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRUZ-REEL7 | 功能描述:IC ADC BRIDGE TRANSDUCER 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRZ | 功能描述:IC ADC BRIDGE TRANSDUCER 24-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRZ | 制造商:Analog Devices 功能描述:IC, ADC, 24BIT, 1.2KSPS, SOIC-24 |

发布紧急采购,3分钟左右您将得到回复。