- 您现在的位置:买卖IC网 > PDF目录10143 > AD9240ASZRL (Analog Devices Inc)IC ADC 14BIT 10MSPS 44-MQFP TR PDF资料下载

参数资料

| 型号: | AD9240ASZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 23/24页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT 10MSPS 44-MQFP TR |

| 标准包装: | 800 |

| 位数: | 14 |

| 采样率(每秒): | 10M |

| 数据接口: | 并联 |

| 转换器数目: | 7 |

| 功率耗散(最大): | 330mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-QFP |

| 供应商设备封装: | 44-MQFP(10x10) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 2 个单端,单极;1 个差分,单极 |

AD9240

REV.

–8–

CLOCK FREQUENCY – MHz

SINAD

–

dB

80

20

120

10

70

60

50

40

30

10

0

RBIAS = 10k

RBIAS = 20k

RBIAS = 200k

RBIAS =

4k

RBIAS =

2k

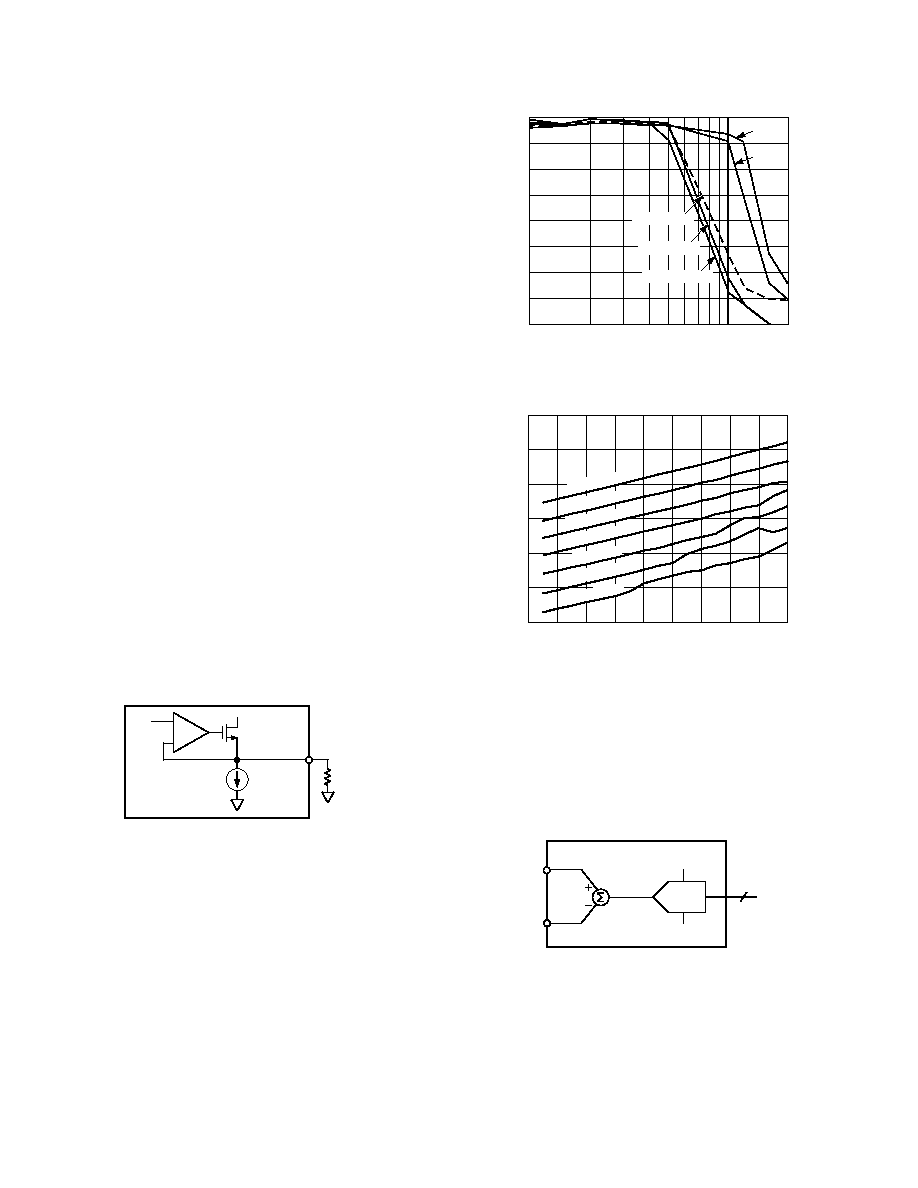

Figure 21. SINAD vs. Clock Frequency for Varying RBIAS

Values (VCM = 2.5 V, AIN = –0.5 dB, 5 V Span, fIN = fCLK/2)

CLOCK FREQUENCY – MHz

POWER

–

mW

400

100

220

4

6

8

10

12

14

16

18

350

300

250

200

150

RBIAS

= 1.7k

RBIAS

= 2k

RBIAS

= 2.5k

RBIAS

= 3.3k

RBIAS

= 5k

RBIAS

= 10k

RBIAS

= 100k

Figure 22. Power Dissipation vs. Clock Frequency for

Varying RBIAS Values

ANALOG INPUT AND REFERENCE OVERVIEW

Figure 23, a simplified model of the AD9240, highlights the rela-

tionship between the analog inputs, VINA, VINB, and the ref-

erence voltage, VREF. Like the voltage applied to the top of

the resistor ladder in a flash A/D converter, the value VREF defines

the maximum input voltage to the A/D core. The minimum input

voltage to the A/D core is automatically defined to be –VREF.

VCORE

VINA

VINB

+VREF

–VREF

A/D

CORE

14

AD9240

Figure 23. Equivalent Functional Input Circuit

INTRODUCTION

The AD9240 uses a four-stage pipeline architecture with a

wideband input sample-and-hold amplifier (SHA) implemented

on a cost-effective CMOS process. Each stage of the pipeline,

excluding the last, consists of a low resolution flash A/D con-

nected to a switched capacitor DAC and interstage residue

amplifier (MDAC). The residue amplifier amplifies the differ-

ence between the reconstructed DAC output and the flash input

for the next stage in the pipeline. One bit of redundancy is used

in each of the stages to facilitate digital correction of flash er-

rors. The last stage simply consists of a flash A/D.

The pipeline architecture allows a greater throughput rate at the

expense of pipeline delay or latency. This means that while the

converter is capable of capturing a new input sample every clock

cycle, it actually takes three clock cycles for the conversion to be

fully processed and appear at the output. This latency is not a

concern in most applications. The digital output, together with

the out-of-range indicator (OTR), is latched into an output

buffer to drive the output pins. The output drivers can be con-

figured to interface with +5 V or +3.3 V logic families.

The AD9240 uses both edges of the clock in its internal timing

circuitry (see Figure 1 and specification page for exact timing

requirements). The A/D samples the analog input on the rising

edge of the clock input. During the clock low time (between the

falling edge and rising edge of the clock), the input SHA is in

the sample mode; during the clock high time it is in the hold

mode. System disturbances just prior to the rising edge of the

clock and/or excessive clock jitter may cause the input SHA to

acquire the wrong value, and should be minimized.

Speed/Power Programmability

The AD9240’s maximum conversion rate and associated power

dissipation can be set using the part’s BIAS pin. A simplified

diagram of the on-chip circuitry associated with the BIAS pin is

shown in Figure 20.

AD9240

BIAS

RBIAS

IFIXED

ADCBIAS

Figure 20.

The value of RBIAS can be varied over a limited range to set the

maximum sample rate and power dissipation of the AD9240. A

typical plot of S/(N+D) @ fIN = Nyquist vs. fCLK at varying

RBIAS is shown in Figure 21. A similar plot of power vs. fCLK

at varying RBIAS is shown in Figure 22. These plots indicate

typical performance vs. RBIAS. Note that all other plots and

specifications in this data sheet reflect performance at a fixed

RBIAS = 2 k

.

B

相关PDF资料 |

PDF描述 |

|---|---|

| IDT7201LA25SOI8 | IC MEM FIFO 512X9 25NS 28-SOIC |

| AD7880CRZ-REEL | IC ADC 12BIT MONO LP 24-SOIC |

| VI-222-IW-F4 | CONVERTER MOD DC/DC 15V 100W |

| LTC1604CG#TR | IC ADC 16BIT SAMPL SHTDWN 36SSOP |

| VE-2NX-MX-F3 | CONVERTER MOD DC/DC 5.2V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9240EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 14-Bit, 10 MSPS Monolithic A/D Converter |

| AD9240-EB | 制造商:Analog Devices 功能描述: |

| AD9241 | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 14-Bit, 1.25 MSPS Monolithic A/D Converter |

| AD9241ACHIPS | 制造商:Analog Devices 功能描述: |

| AD9241AS | 制造商:Analog Devices 功能描述:ADC Single Pipelined 1.25Msps 14-bit Parallel 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:14BIT 1.25 MSPS MONOLITHIC A/D CONVERTER - Bulk 制造商:Analog Devices 功能描述:IC 14-BIT ADC |

发布紧急采购,3分钟左右您将得到回复。