- 您现在的位置:买卖IC网 > PDF目录10143 > AD9240ASZRL (Analog Devices Inc)IC ADC 14BIT 10MSPS 44-MQFP TR PDF资料下载

参数资料

| 型号: | AD9240ASZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/24页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT 10MSPS 44-MQFP TR |

| 标准包装: | 800 |

| 位数: | 14 |

| 采样率(每秒): | 10M |

| 数据接口: | 并联 |

| 转换器数目: | 7 |

| 功率耗散(最大): | 330mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-QFP |

| 供应商设备封装: | 44-MQFP(10x10) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 2 个单端,单极;1 个差分,单极 |

AD9240

REV.

–11–

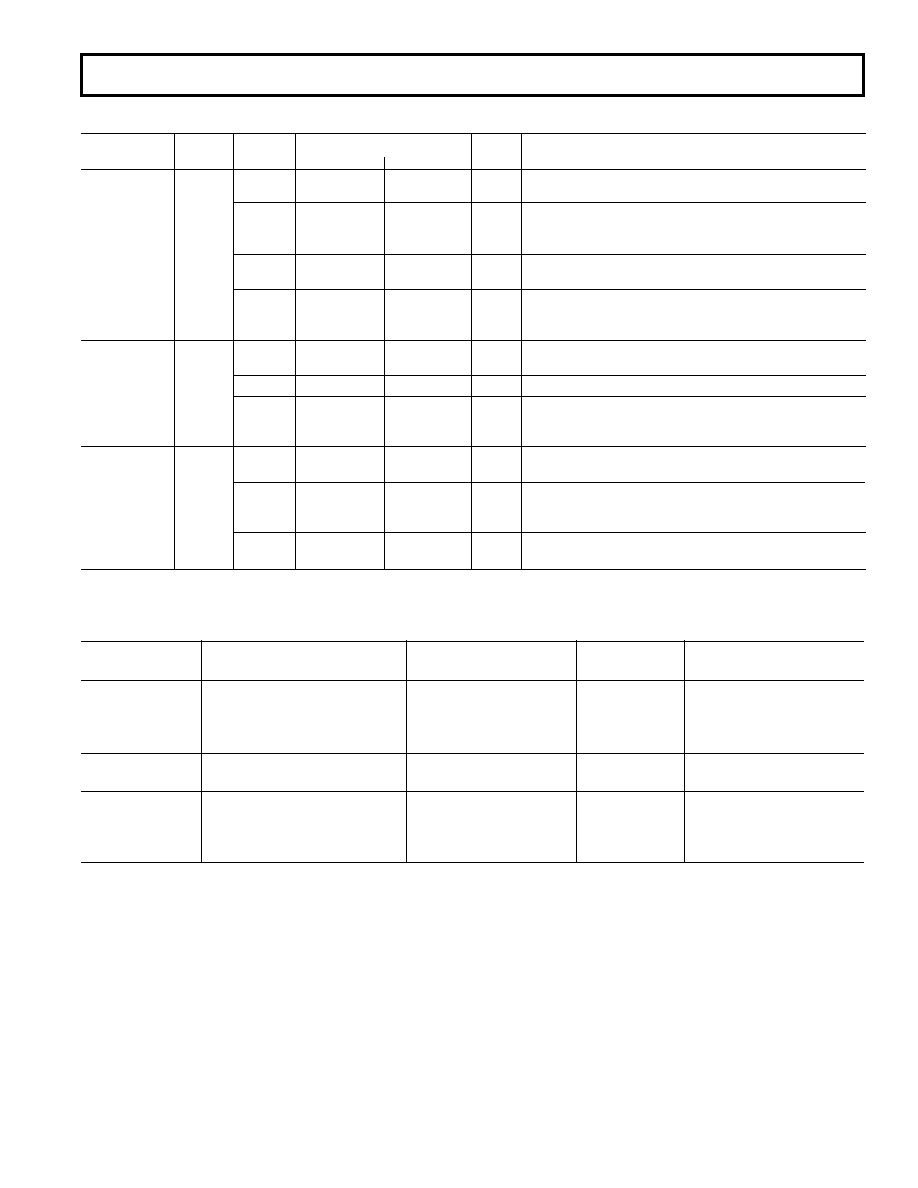

Table I. Analog Input Configuration Summary

Input

Input Range (V)

Figure

Connection

Coupling

Span (V)

VINA

1

VINB

1

#

Comments

Single-Ended

DC

2

0 to 2

1

32, 33

Best for stepped input response applications, suboptimum THD

and noise performance, requires

±5 V op amp.

2

× VREF

0 to

VREF

32, 33

Same as above but with improved noise performance due to

2

× VREF

increase in dynamic range. Headroom/settling time requirements

of

±5 V op amp should be evaluated.

5

0 to 5

2.5

32, 33

Optimum noise performance, excellent THD performance. Requires

op amp with VCC > +5 V due to insufficient headroom @ 5 V.

2

× VREF

2.5 – VREF

2.5

39

Optimum THD performance with VREF = 1, noise performance

to

improves while THD performance degrades as VREF increases

2.5 + VREF

to 2.5 V. Single supply operation (i.e., +5 V) for many op amps.

Single-Ended

AC

2 or

0 to 1 or

1 or VREF

34

Suboptimum ac performance due to input common-mode level

2

× VREF

0 to 2

× VREF

not biased at optimum midsupply level (i.e., 2.5 V).

5

0 to 5

2.5

34

Optimum noise performance, excellent THD performance.

2

× VREF

2.5 – VREF

2.5

35

Flexible input range, Optimum THD performance with VREF = 1.

to

Noise performance improves while THD performance degrades as

2.5 + VREF

VREF increases to 2.5 V.

Differential

AC or

2

2 to 3

3 to 2

29–31

Optimum full-scale THD and SFDR performance well beyond the

DC

A/Ds Nyquist frequency.

2

× VREF

2.5 – VREF/2

2.5 + VREF/2

29–31

Same as 2 V to 3 V input range with the exception that full-scale

to

THD and SFDR performance can be traded off for better noise

2.5 + VREF/2

2.5 – VREF/2

performance.

5

1.25 to 3.75

3.75 to 1.25

29–31

Widest dynamic range (i.e., ENOBs) due to optimum noise

performance.

1VINA and VINB can be interchanged if signal inversion is required.

Table II. Reference Configuration Summary

Reference

Input Span (VINA–VINB)

Operating Mode

(V p-p)

Required VREF (V)

Connect

To

INTERNAL

2

1

SENSE

VREF

INTERNAL

5

2.5

SENSE

REFCOM

INTERNAL

2

≤ SPAN ≤ 5 AND

1

≤ VREF ≤ 2.5 AND

R1

VREF AND SENSE

SPAN = 2

× VREF

VREF = (1 + R1/R2)

R2

SENSE AND REFCOM

EXTERNAL

2

≤ SPAN ≤ 51 ≤ VREF ≤ 2.5

SENSE

AVDD

(NONDYNAMIC)

VREF

EXT. REF.

EXTERNAL

2

≤ SPAN ≤ 5

CAPT and CAPB

SENSE

AVDD

(DYNAMIC)

Externally Driven

VREF

REFCOM

EXT. REF. 1

CAPT

EXT. REF. 2

CAPB

B

相关PDF资料 |

PDF描述 |

|---|---|

| IDT7201LA25SOI8 | IC MEM FIFO 512X9 25NS 28-SOIC |

| AD7880CRZ-REEL | IC ADC 12BIT MONO LP 24-SOIC |

| VI-222-IW-F4 | CONVERTER MOD DC/DC 15V 100W |

| LTC1604CG#TR | IC ADC 16BIT SAMPL SHTDWN 36SSOP |

| VE-2NX-MX-F3 | CONVERTER MOD DC/DC 5.2V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9240EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 14-Bit, 10 MSPS Monolithic A/D Converter |

| AD9240-EB | 制造商:Analog Devices 功能描述: |

| AD9241 | 制造商:AD 制造商全称:Analog Devices 功能描述:Complete 14-Bit, 1.25 MSPS Monolithic A/D Converter |

| AD9241ACHIPS | 制造商:Analog Devices 功能描述: |

| AD9241AS | 制造商:Analog Devices 功能描述:ADC Single Pipelined 1.25Msps 14-bit Parallel 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:14BIT 1.25 MSPS MONOLITHIC A/D CONVERTER - Bulk 制造商:Analog Devices 功能描述:IC 14-BIT ADC |

发布紧急采购,3分钟左右您将得到回复。