- 您现在的位置:买卖IC网 > PDF目录10047 > AD9246BCPZRL7-125 (Analog Devices Inc)IC ADC 14BIT 125MSPS 48-LFCSP PDF资料下载

参数资料

| 型号: | AD9246BCPZRL7-125 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 42/44页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT 125MSPS 48-LFCSP |

| 设计资源: | Using AD8376 to Drive Wide Bandwidth ADCs for High IF AC-Coupled Appls (CN0002) Driving AD9233/46/54 ADCs in AC-Coupled Baseband Appls (CN0051) |

| 标准包装: | 750 |

| 位数: | 14 |

| 采样率(每秒): | 125M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 3 |

| 功率耗散(最大): | 425mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP-VQ(7x7) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 2 个单端,单极;1 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页

AD9246

Rev. A | Page 7 of 44

SWITCHING SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 2.5 V, unless otherwise noted.

Table 4.

AD9246BCPZ-80

AD9246BCPZ-105

AD9246BCPZ-125

Temp

Min

Typ

Max

Min

Typ

Max

Min

Typ

Max

Unit

CLOCK INPUT PARAMETERS

Conversion Rate, DCS Enabled

Full

20

80

20

105

20

125

MSPS

Conversion Rate, DCS Disabled

Full

10

80

10

105

10

125

MSPS

CLK Period

Full

12.5

9.5

8

ns

CLK Pulse Width High, DCS Enabled

Full

3.75

6.25

8.75

2.85

4.75

6.65

2.4

4

5.6

ns

CLK Pulse Width High, DCS Disabled

Full

5.63

6.25

6.88

4.28

4.75

5.23

3.6

4

4.4

ns

DATA OUTPUT PARAMETERS

Full

3.1

3.9

4.8

3.1

3.9

4.8

3.1

3.9

4.8

ns

DCO Propagation Delay (tDCO)

Full

4.4

ns

Setup Time (tS)

Full

4.9

5.7

3.4

4.3

2.6

3.5

ns

Hold Time (tH)

Full

5.9

6.8

4.4

5.3

3.7

4.5

ns

Pipeline Delay (Latency)

Full

12

cycles

Aperture Delay (tA)

Full

0.8

ns

Aperture Uncertainty (Jitter, tJ)

Full

0.1

ps rms

Full

350

μs

OUT-OF-RANGE RECOVERY TIME

Full

2

3

Cycles

SCLK Period (tCLK)

Full

40

ns

SCLK Pulse Width High Time (tHI)

Full

16

ns

SCLK Pulse Width Low Time (tLO)

Full

16

ns

SDIO to SCLK Setup Time (tDS)

Full

5

ns

SDIO to SCLK Hold Time (tDH)

Full

2

ns

CSB to SCLK Setup Time (tS)

Full

5

ns

CSB to SCLK Hold Time (tH)

Full

2

ns

1 See AN-835, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions.

2 Output propagation delay is measured from CLK 50% transition to DATA 50% transition, with 5 pF load.

3 Wake-up time is dependent on the value of the decoupling capacitors, values shown with 0.1 μF capacitor across REFT and REFB.

4 See Figure 57 and the Serial Port Interface (SPI) section.

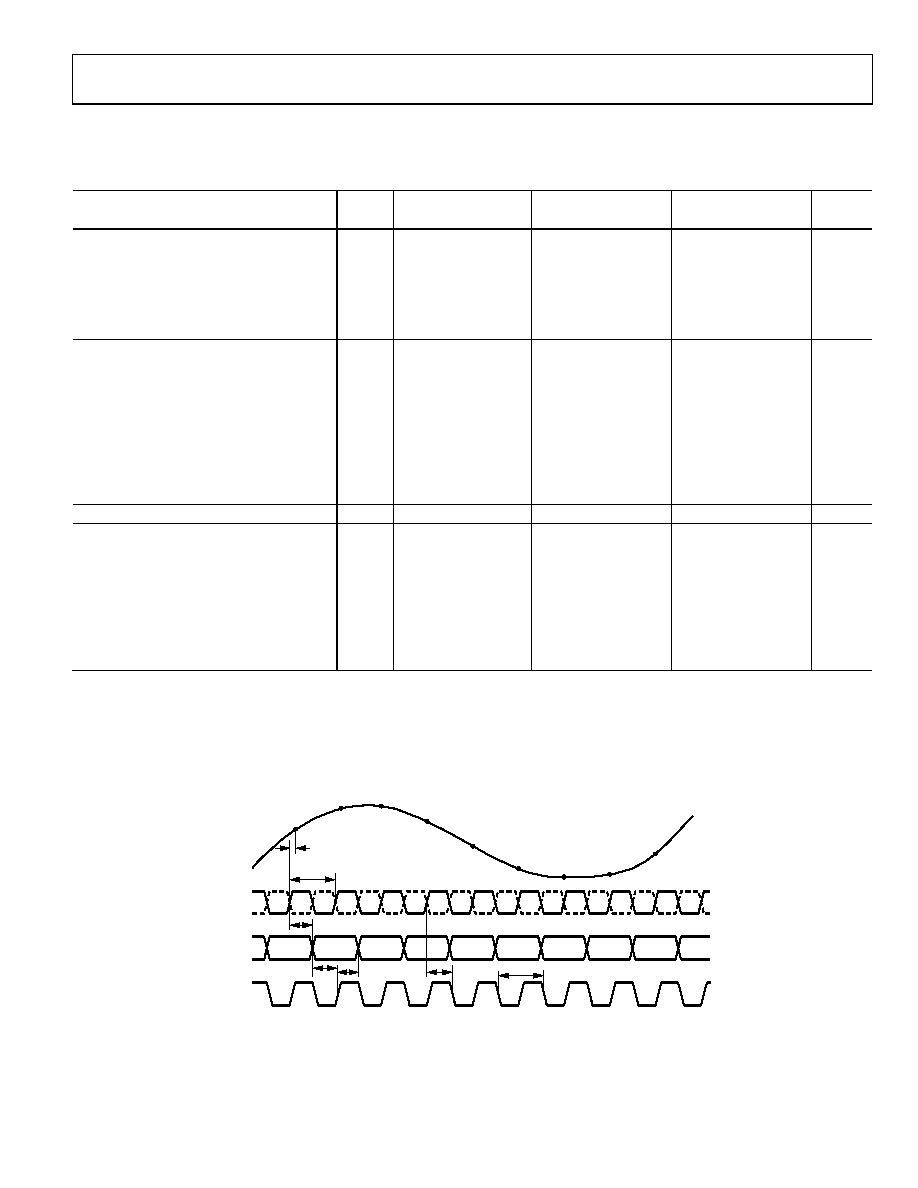

TIMING DIAGRAM

CLK+

DCO

DATA

N

N+ 1

N+ 2

N+ 3

N+ 4

N+ 5

N+ 6

N+ 7

N+ 8

N – 12

N – 11

N – 10

N – 9

N – 8

N – 7

N – 6

N – 5

N – 4

N – 13

CLK–

tCLK

tPD

tS

tH

tDCO

tCLK

tA

05

49

1-

0

02

Figure 2. Timing Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| MS27473T12C98S | CONN PLUG 10POS STRAIGHT W/SCKT |

| MS27497T24F61S | CONN RCPT 61POS WALL MNT W/SCKT |

| VI-2VV-MY | CONVERTER MOD DC/DC 5.8V 50W |

| VI-2VT-MY | CONVERTER MOD DC/DC 6.5V 50W |

| VI-B03-MY | CONVERTER MOD DC/DC 24V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9246BCPZRL7-80 | 制造商:Analog Devices 功能描述:14-BIT, 80 MSPS/105 MSPS/125 MSPS, 1.8 V ANALOG-TO-DIGITAL C - Tape and Reel |

| AD9248 | 制造商:Analog Devices 功能描述:40 MSPS DUAL A/D CONVERTER - Bulk |

| AD9248-20PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 20/40/65 MSPS Dual A/ D Converter |

| AD9248-40PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 20/40/65 MSPS Dual A/ D Converter |

| AD9248-65PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:14-Bit, 20/40/65 MSPS Dual A/ D Converter |

发布紧急采购,3分钟左右您将得到回复。