参数资料

| 型号: | AD9513BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/28页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK DIST 3OUT PLL 32LFCSP |

| 标准包装: | 1 |

| 类型: | 扇出缓冲器(分配),除法器 |

| PLL: | 无 |

| 输入: | 时钟 |

| 输出: | CMOS,LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:3 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 800MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 托盘 |

| 产品目录页面: | 776 (CN2011-ZH PDF) |

| 配用: | AD9513/PCBZ-ND - BOARD EVAL FOR AD9513 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD9513

Rev. 0 | Page 20 of 28

Table 16. OUT0 Divide or OUT2 Divide

S9

S10

OUT0

Divide (Duty Cycle1)

S2 ≠ 2/3

OUT2

Divide (Duty Cycle1)

S2 = 2/3

0

1

7 (43%)

1/3

0

2 (50%)

11 (45%)

2/3

0

3 (33%)

13 (46%)

1

0

4 (50%)

14 (50%)

0

1/3

5 (40%)

17 (47%)

1/3

6 (50%)

19 (47%)

2/3

1/3

8 (50%)

20 (50%)

1

1/3

9 (44%)

21 (48%)

0

2/3

10 (50%)

22 (50%)

1/3

2/3

12 (50%)

23 (48%)

2/3

15 (47%)

25 (48%)

1

2/3

16 (50%)

26 (50%)

0

1

18 (50%)

27 (48%)

1/3

1

24 (50%)

28 (50%)

2/3

1

30 (50%)

29 (48%)

1

32 (50%)

31 (48%)

1 Duty cycle is the clock signal high time divided by the total period.

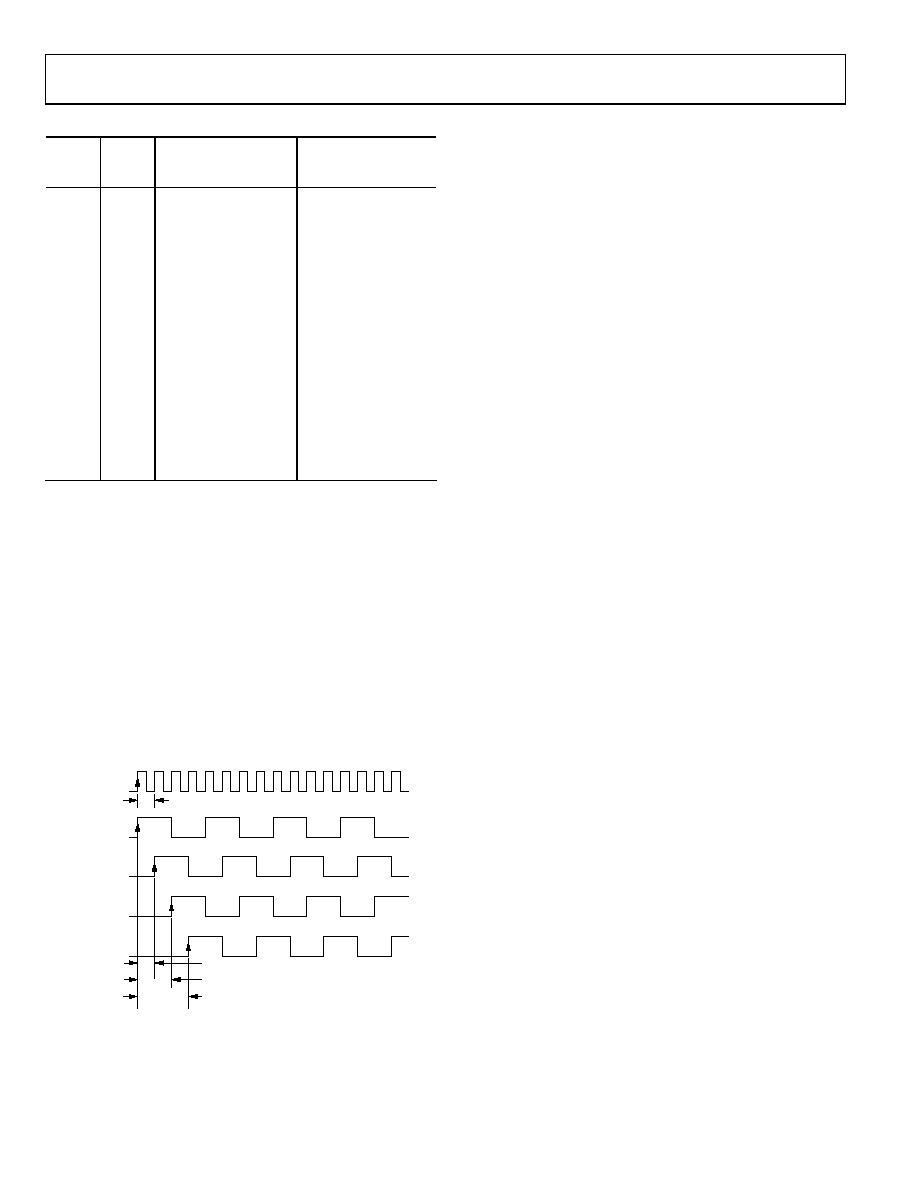

DIVIDER PHASE OFFSET

The phase offset of OUT1 and OUT2 can be selected (see Table 13

to Table 15). This allows the relative phase of the outputs to be set.

After a SYNC operation (see the Synchronization section), the

phase offset word of each divider determines the number of

input clock (CLK) cycles to wait before initiating a clock output

edge. By giving each divider a different phase offset, output-to-

output delays can be set in increments of the fast clock period, tCLK.

Figure 24 shows four cases, each with the divider set to divide = 4.

By incrementing the phase offset from 0 to 3, the output is

offset from the initial edge by a multiple of tCLK.

01

4

123

5

9

67

8

10

14

11 12 13

5

tCLK

CLOCK INPUT

CLK

DIVIDER OUTPUT

DIV = 4

PHASE = 0

PHASE = 1

PHASE = 2

PHASE = 3

tCLK

2 × tCLK

3 × tCLK

05

59

5-

02

4

Figure 24. Phase Offset—Divider Set for Divide = 4, Phase Set from 0 to 2

For example:

CLK = 491.52 MHz

tCLK = 1/491.52 = 2.0345 ns

For Divide = 4:

Phase Offset 0 = 0 ns

Phase Offset 1 = 2.0345 ns

Phase Offset 2 = 4.069 ns

Phase Offset 3 = 6.104 ns

The outputs can also be described as:

Phase Offset 0 = 0°

Phase Offset 1 = 90°

Phase Offset 2 = 180°

Phase Offset 3 = 270°

Setting the phase offset to Phase = 4 results in the same relative

phase as Phase = 0° or 360°.

The resolution of the phase offset is set by the fast clock period

(tCLK) at CLK. The maximum unique phase offset is less than the

divide ratio, up to a phase offset of 15.

Phase offsets can be related to degrees by calculating the phase

step for a particular divide ratio:

Phase Step = 360°/Divide Ratio

Using some of the same examples:

Divide = 4

Phase Step = 360°/4 = 90°

Unique Phase Offsets in Degrees Are Phase = 0°, 90°,

180°, 270°

Divide = 9

Phase Step = 360°/9 = 40°

Unique Phase Offsets in Degrees Are Phase = 0°, 40°, 80°,

120°, 160°, 200°, 240°, 280°, 320°

相关PDF资料 |

PDF描述 |

|---|---|

| SY10E167JZ | IC MUX/REGISTER 6BIT 2:1 28PLCC |

| AD9572ACPZLVD | IC PLL CLOCK GEN 25MHZ 40LFCSP |

| SY89546UMG | IC MUX 4:1 LVDS DIFF 2.5V 32MLF |

| AD9552BCPZ | IC PLL CLOCK GEN LP 32LFCSP |

| VE-JVR-MZ-S | CONVERTER MOD DC/DC 7.5V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9513BCPZ-REEL7 | 功能描述:IC CLOCK DIST 3OUT PLL 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| AD9514 | 制造商:AD 制造商全称:Analog Devices 功能描述:1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Three Outputs |

| AD9514/PCB | 制造商:Analog Devices 功能描述:CLOCK DISTRIBUTION - Bulk |

| AD9514/PCBZ | 功能描述:BOARD EVAL CLOCK 3CH AD9514 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| AD9514BCPZ | 功能描述:IC CLOCK DIST 3OUT PLL 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

发布紧急采购,3分钟左右您将得到回复。