- 您现在的位置:买卖IC网 > PDF目录1987 > AD9520-5BCPZ-REEL7 (Analog Devices Inc)IC CLOCK GEN EXT VCO 64LFCSP PDF资料下载

参数资料

| 型号: | AD9520-5BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 4/76页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN EXT VCO 64LFCSP |

| 设计资源: | Synchronizing Multiple AD9910 1 GSPS Direct Digital Synthesizers (CN0121) Phase Coherent FSK Modulator (CN0186) |

| 标准包装: | 750 |

| 类型: | 时钟发生器,扇出配送 |

| PLL: | 是 |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:12,2:24 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 2.4GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

AD9520-5

Data Sheet

Rev. A | Page 12 of 76

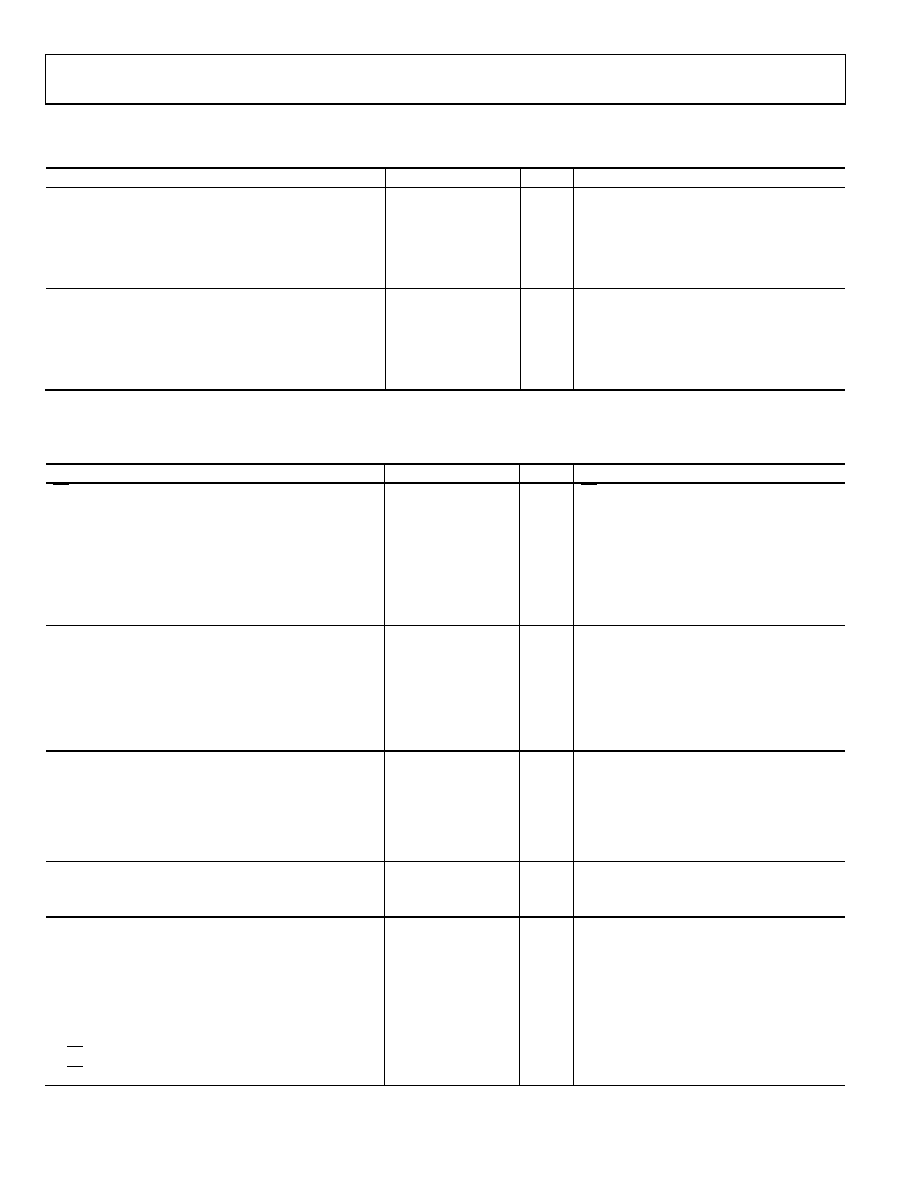

CLOCK OUTPUT ADDITIVE TIME JITTER (VCO DIVIDER USED)

Table 9.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

LVPECL OUTPUT ADDITIVE TIME JITTER

Distribution section only; does not include PLL;

uses rising edge of clock signal

CLK = 1.0 GHz; VCO DIV = 5; LVPECL = 100 MHz;

Channel Divider = 2; Duty-Cycle Correction = Off

230

fs rms

Calculated from SNR of ADC method

(broadband jitter)

CLK = 500 MHz; VCO DIV = 5; LVPECL = 100 MHz;

Bypass Channel Divider; Duty-Cycle Correction = On

215

fs rms

Calculated from SNR of ADC method

(broadband jitter)

CMOS OUTPUT ADDITIVE TIME JITTER

Distribution section only; does not include PLL;

uses rising edge of clock signal

CLK = 200 MHz; VCO DIV = 2; CMOS = 100 MHz;

Bypass Channel Divider; Duty-Cycle Correction = Off

326

fs rms

Calculated from SNR of ADC method

(broadband jitter)

CLK = 1600 MHz; VCO DIV = 2; CMOS = 100 MHz;

Channel Divider = 8; Duty-Cycle Correction = Off

362

fs rms

Calculated from SNR of ADC method

(broadband jitter)

SERIAL CONTROL PORT—SPI MODE

Table 10.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

CS (INPUT)

CS has an internal 30 kΩ pull-up resistor

Input Logic 1 Voltage

2.0

V

Input Logic 0 Voltage

0.8

V

Input Logic 1 Current

3

A

Input Logic 0 Current

110

A

The minus sign indicates that current is

flowing out of the AD9520, which is due to

the internal pull-up resistor

Input Capacitance

2

pF

SCLK (INPUT) IN SPI MODE

SCLK has an internal 30 kΩ pull-down resistor

in SPI mode, but not in I2C mode

Input Logic 1 Voltage

2.0

V

Input Logic 0 Voltage

0.8

V

Input Logic 1 Current

110

A

Input Logic 0 Current

1

A

Input Capacitance

2

pF

SDIO (INPUT IN BIDIRECTIONAL MODE)

Input Logic 1 Voltage

2.0

V

Input Logic 0 Voltage

0.8

V

Input Logic 1 Current

1

A

Input Logic 0 Current

1

A

Input Capacitance

2

pF

SDIO, SDO (OUTPUTS)

Output Logic 1 Voltage

2.7

V

Output Logic 0 Voltage

0.4

V

TIMING

Clock Rate (SCLK, 1/tSCLK)

25

MHz

Pulse Width High, tHIGH

16

ns

Pulse Width Low, tLOW

16

ns

SDIO to SCLK Setup, tDS

4

ns

SCLK to SDIO Hold, tDH

0

ns

SCLK to Valid SDIO and SDO, tDV

11

ns

CS to SCLK Setup and Hold, tS, tC

2

ns

CS Minimum Pulse Width High, tPWH

3

ns

相关PDF资料 |

PDF描述 |

|---|---|

| AD9522-0BCPZ-REEL7 | IC CLOCK GEN 2.8GHZ VCO 64LFCSP |

| AD9522-1BCPZ-REEL7 | IC CLOCK GEN 2.5GHZ VCO 64LFCSP |

| AD9522-2BCPZ | IC CLOCK GEN 2.2GHZ VCO 64LFCSP |

| AD9522-3BCPZ-REEL7 | IC CLOCK GEN 2GHZ VCO 64LFCSP |

| AD9522-4BCPZ-REEL7 | IC CLOCK GEN 1.6GHZ VCO 64LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9521JH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Log/Antilog Amplifier |

| AD9521KH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Log/Antilog Amplifier |

| AD9521SE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Log/Antilog Amplifier |

| AD9521SH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Log/Antilog Amplifier |

| AD9521TE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Log/Antilog Amplifier |

发布紧急采购,3分钟左右您将得到回复。