参数资料

| 型号: | AD9540BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 31/32页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GENERATOR PLL 48-LFCSP |

| 标准包装: | 1 |

| 类型: | 时钟发生器 |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | CML,PECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 655MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP-VQ(7x7) |

| 包装: | 托盘 |

| 产品目录页面: | 776 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页

AD9540

Rev. A | Page 8 of 32

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

51.84 MHz FOUT

@ 10 Hz Offset

110

dBc/Hz

@ 100 Hz Offset

121

dBc/Hz

@ 1 kHz Offset

135

dBc/Hz

@ 10 kHz Offset

142

dBc/Hz

@ 100 kHz Offset

148

dBc/Hz

> 1 MHz Offset

153

dBc/Hz

105 MHz Analog Out

@ 10 Hz Offset

105

dBc/Hz

@ 100 Hz Offset

115

dBc/Hz

@ 1 kHz Offset

126

dBc/Hz

@ 10 kHz Offset

132

dBc/Hz

@ 100 kHz Offset

140

dBc/Hz

>1 MHz Offset

145

dBc/Hz

155.52 MHz Analog Out

@ 10 Hz Offset

100

dBc/Hz

@ 100 Hz Offset

112

dBc/Hz

@ 1 kHz Offset

123

dBc/Hz

@ 10 kHz Offset

131

dBc/Hz

@ 100 kHz Offset

138

dBc/Hz

>1 MHz Offset

144

dBc/Hz

1 The SNR of a 14-bit ADC was measured with an ENCODE rate of 105 MSPS and an AIN of 170 MHz. The resultant SNR was known to be limited by the jitter of the clock,

not by the noise on the AIN signal. From this SNR value, the jitter affecting the measurement can be back calculated.

2 Driving the REFIN input buffer. The crystal oscillator section of this input stage performs up to only 30 MHz.

3 The charge pump output compliance range is functionally 0.2 V to (CP_VDD 0.2 V). The value listed here is the compliance range for 5% matching.

4 The input impedance of the CLK1 input is 1500 . However, to provide matching on the clock line, an external 50 load is used.

5 Measured as peak-to-peak between DAC outputs.

6 For a 4.02 k resistor from DRV_RSET to GND.

7 Assumes a 1 mA load.

LOOP MEASUREMENT CONDITIONS

622 MHz OC-12 Clock

VCO = Sirenza 190-640T

Reference = Wenzel 500-10116 (30.3 MHz)

Loop Filter = 10 kHz BW, 60° Phase Margin

C1 = 170 nF, R1 = 14.4 , C2 = 5.11 F, R2 = 89.3 ,

C3 Omitted

CP_OUT = 4 mA (Scaler = ×8)

÷R = 2, ÷M = 1, ÷N = 1

105 MHz Converter Clock

VCO = Sirenza 190-845T

Reference = Wenzel 500-10116 (30.3 MHz)

Loop Filter = 10 kHz BW, 45° Phase Margin

C1 = 117 nF, R1 = 28 , C2 = 1.6 F, R2 = 57.1 , C3 = 53.4 nF

CP_OUT = 4 mA (Scaler = ×8)

÷R = 8, ÷M = 1, ÷N = 1

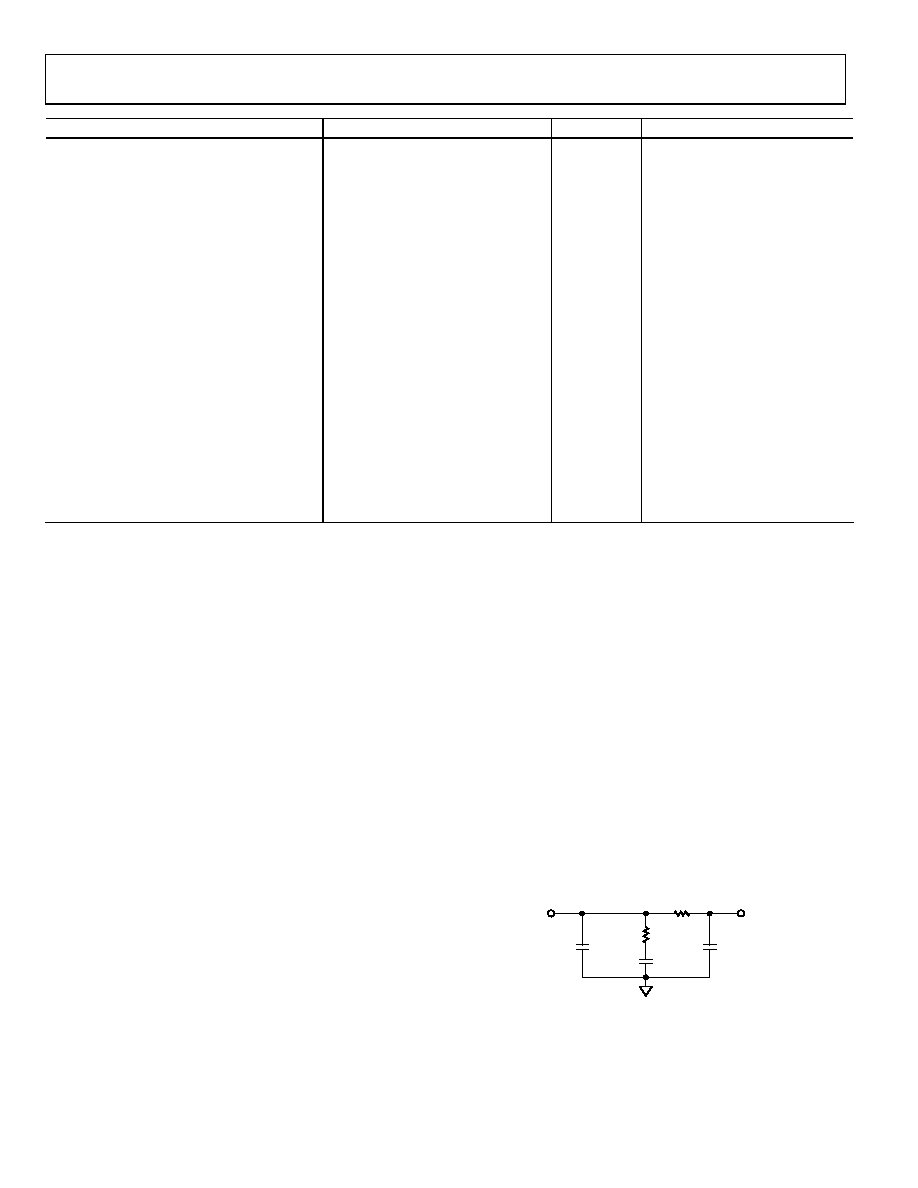

C1

C3

INPUT

OUTPUT

C2

R1

R2

04947-

041

Figure 2. Generic Loop Filter

相关PDF资料 |

PDF描述 |

|---|---|

| X9317WM8IZ | IC XDCP SGL 100TAP 10K 8-MSOP |

| X9317UV8IZ | IC XDCP 100TAP 50K 3-WIRE 8TSSOP |

| M83723/76A20257 | CONN PLUG 25POS STRAIGHT W/PINS |

| M83723/76A20256 | CONN PLUG 25POS STRAIGHT W/PINS |

| X9317UM8IZ | IC XDCP 100TAP 10K 3-WIRE 8-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9540BCPZ-REEL | 制造商:AD 制造商全称:Analog Devices 功能描述:655 MHz Low Jitter Clock Generator |

| AD9540BCPZ-REEL7 | 功能描述:IC CLOCK GEN/SYNTHESIZER 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| AD9540PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:655 MHz Low Jitter Clock Generator |

| AD9540-VCO/PCB | 制造商:Analog Devices 功能描述:EVAL BD FOR AD9540 ,655 MHZ LOW JITTER CLOCK GEN - Trays |

| AD9540-VCO/PCBZ | 功能描述:BOARD EVAL CLK GEN SYNTH 48LFCSP RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。