- 您现在的位置:买卖IC网 > PDF目录10034 > AD9640ABCPZ-105 (Analog Devices Inc)IC ADC 14BIT 105MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9640ABCPZ-105 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 41/52页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT 105MSPS 64LFCSP |

| 设计资源: | Interfacing ADL5534 to AD9640 High Speed ADC (CN0049) |

| 标准包装: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 105M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 657mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

AD9640

Rev. B | Page 46 of 52

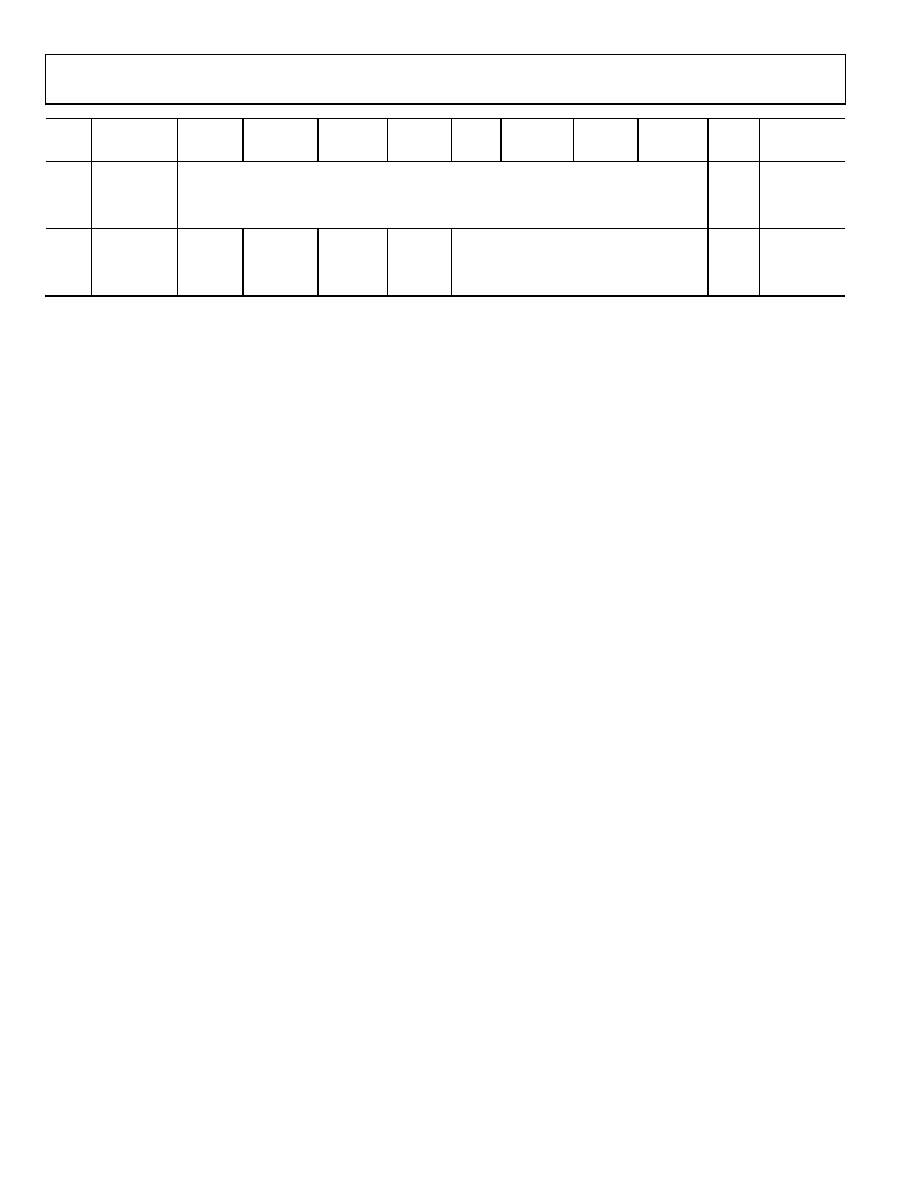

Addr

(Hex)

Register

Name

Bit 7

(MSB)

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

(LSB)

Default

Value

(Hex)

Default

Notes/

Comments

0x11A

Signal Monitor

Result

Channel B

Register 1

(Global)

Signal Monitor Result Channel B[15:8]

Read only

0x11B

Signal Monitor

Result

Channel B

Register 2

(Global)

Open

Signal Monitor Result Channel B[19:16]

Read only

MEMORY MAP REGISTER DESCRIPTION

For additional information about functions controlled in

Register 0x00 to Register 0xFF, see the AN-877 Application Note,

Interfacing to High Speed ADCs via SPI.

Sync Control (Register 0x100)

Bit 7—Signal Monitor Sync Enable

Bit 7 enables the sync pulse from the external SYNC input to

the signal monitor block. The sync signal is passed when Bit 7

is high and Bit 0 is high. This is continuous sync mode.

Bits[6:3]—Reserved

Bit 2—Clock Divider Next Sync Only

If the sync enable bit (Address 0x100[0]) is high and the clock

divider sync enable (Address 0x100[1]) is high, Bit 2 allows the

clock divider to sync to the first sync pulse it receives and ignore

the rest. Address 0x100[1] resets after it syncs.

Bit 1—Clock Divider Sync Enable

Bit 1 gates the sync pulse to the clock divider. The sync signal is

passed when Bit 1 is high and Bit 0 is high. This is continuous

sync mode.

Bit 0—Master Sync Enable

Bit 0 must be high to enable any of the sync functions.

Fast Detect Control (Register 0x104)

Bits[7:4]—Reserved

Bits[3:1]—Fast Detect Mode Select

These bits set the mode of the fast detect output bits according

to Table 17.

Bit 0—Fast Detect Enable

Bit 0 is used to enable the fast detect bits. When the fast detect

outputs are disabled, the outputs go into a high impedance state.

In LVDS mode, when the outputs are interleaved, the outputs go

high-Z only if both channels are turned off (power-down/standby/

output disabled). If only one channel is turned off (power-down/

standby/output disabled), the fast detect outputs repeat the data

of the active channel.

Fine Upper Threshold (Register 0x106 and Register 0x107)

Register 0x106, Bits[7:0]—Fine Upper Threshold[7:0]

Register 0x107, Bits[7:5]—Reserved

Register 0x107, Bits[4:0]—Fine Upper Threshold[12:8]

These registers provide the fine upper limit threshold. This 13-bit

value is compared to the 13-bit magnitude from the ADC block

and, if the ADC magnitude exceeds this threshold value, the

F_UT flag is set.

Fine Lower Threshold (Register 0x108 and Register 0x109)

Register 0x108, Bits[7:0]—Fine Lower Threshold

[7:0]

Register 0x109, Bits[7:5]—Reserved

Register 0x109, Bits[4:0]—Fine Lower Threshold[12:8]

These registers provide a fine lower limit threshold. This 13-bit

value is compared to the 13-bit magnitude from the ADC block

and, if the ADC magnitude is less than this threshold value, the

F_LT flag is set.

Signal Monitor DC Correction Control (Register 0x10C)

Bit 7—Reserved

Bit 6—DC Correction Freeze

When Bit 6 is set high, the dc correction is no longer updated

to the signal monitoring block. It holds the last dc value it

calculated.

Bits[5:2]—DC Correction Bandwidth

These bits set the averaging time of the signal monitor dc correc-

tion function. It is a 4-bit word that sets the bandwidth of the

correction block (see Table 26).

相关PDF资料 |

PDF描述 |

|---|---|

| MS27467E19B11SA | CONN PLUG 11POS STRAIGHT W/SCKT |

| IDT72805LB10PF8 | IC FIFO SYNC DUAL 256X18 128TQFP |

| VI-J4B-MX-S | CONVERTER MOD DC/DC 95V 75W |

| VI-25D-MX-F2 | CONVERTER MOD DC/DC 85V 75W |

| LTC1350IG#TRPBF | IC TXRX 3.3V EIA/TIA-562 28-SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9640ABCPZ-125 | 功能描述:IC ADC 14BIT 125MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD9640ABCPZ-150 | 功能描述:模数转换器 - ADC 14Bit 150Msps Dual 1.8V PB Free ADC RoHS:否 制造商:Analog Devices 通道数量: 结构: 转换速率: 分辨率: 输入类型: 信噪比: 接口类型: 工作电源电压: 最大工作温度: 安装风格: 封装 / 箱体: |

| AD9640ABCPZ-80 | 功能描述:IC ADC 14BIT 80MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD9640ABCPZRL7-105 | 功能描述:模数转换器 - ADC 14Bit 105Msps Dual 1.8V PB Free ADC RoHS:否 制造商:Analog Devices 通道数量: 结构: 转换速率: 分辨率: 输入类型: 信噪比: 接口类型: 工作电源电压: 最大工作温度: 安装风格: 封装 / 箱体: |

| AD9640ABCPZRL7-125 | 功能描述:14 Bit Analog to Digital Converter 2 Input 2 Pipelined 64-LFCSP-VQ (9x9) 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:在售 位数:14 采样率(每秒):125M 输入数:2 输入类型:差分,单端 数据接口:并联 配置:S/H-ADC 无线电 - S/H:ADC:1:1 A/D 转换器数:2 架构:管线 参考类型:外部, 内部 电压 - 电源,模拟:1.7 V ~ 1.9 V 电压 - 电源,数字:1.7 V ~ 1.9 V 特性:同步采样 工作温度:-40°C ~ 85°C 封装/外壳:64-VFQFN 裸露焊盘,CSP 供应商器件封装:64-LFCSP-VQ(9x9) 标准包装:750 |

发布紧急采购,3分钟左右您将得到回复。