- 您现在的位置:买卖IC网 > PDF目录10034 > AD9640ABCPZ-105 (Analog Devices Inc)IC ADC 14BIT 105MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9640ABCPZ-105 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 42/52页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT 105MSPS 64LFCSP |

| 设计资源: | Interfacing ADL5534 to AD9640 High Speed ADC (CN0049) |

| 标准包装: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 105M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 657mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

AD9640

Rev. B | Page 47 of 52

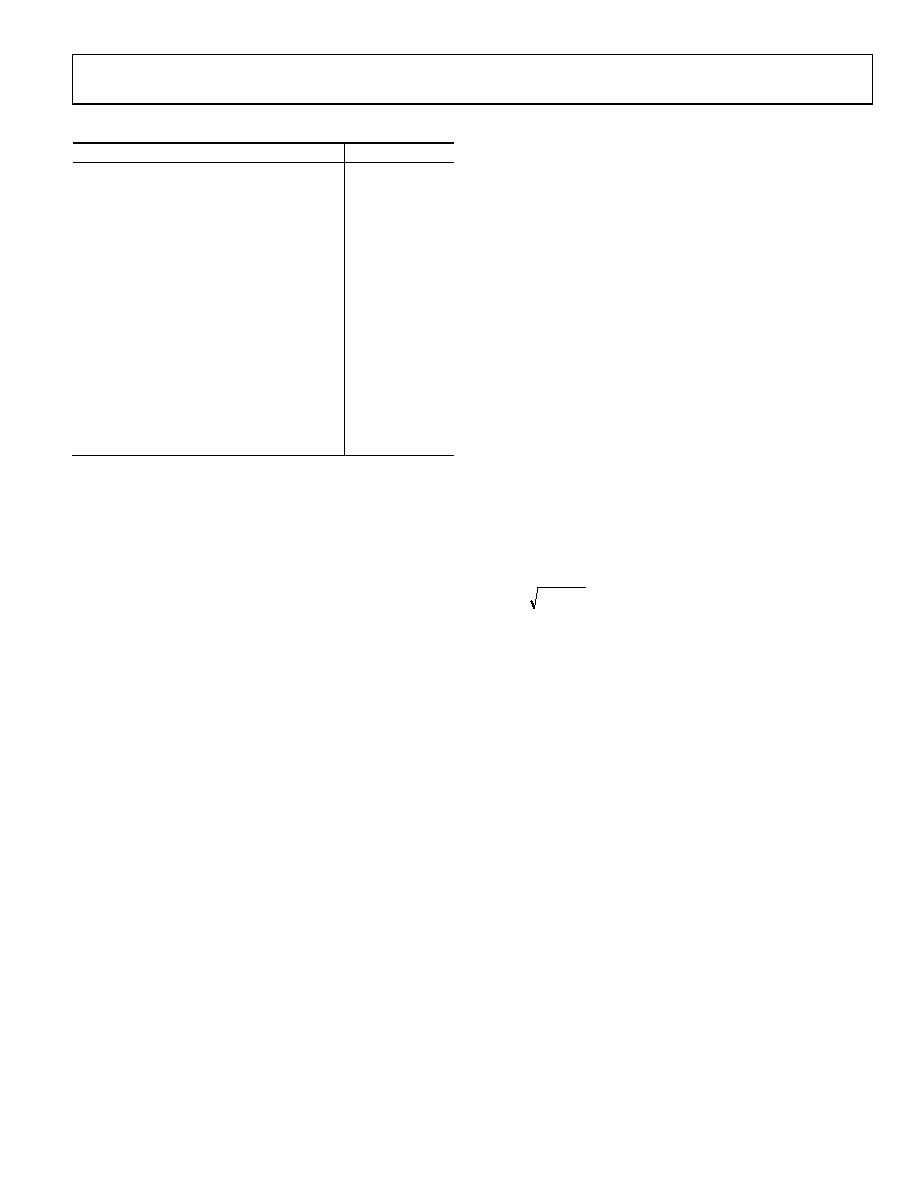

Table 26. DC Correction Bandwidth

DC Correction Control Register 0x10C[5:2]

Bandwidth (Hz)

0000

1218.56

0001

609.28

0010

304.64

0011

152.32

0100

76.16

0101

38.08

0110

19.04

0111

9.52

1000

4.76

1001

2.38

1010

1.19

1011

0.60

1100

0.30

1101

0.15

1110

0.15

1111

0.15

Bit 1—DC Correction for Signal Path Enable

Setting Bit 1 high causes the output of the dc measurement

block to be summed with the data in the signal path to remove

the dc offset from the signal path.

Bit 0—DC Correction for SM Enable

Bit 0 enables the dc correction function in the signal monitoring

block. The dc correction is an averaging function that can be

used by the signal monitor to remove dc offset in the signal.

Removing this dc from the measurement allows a more accurate

reading.

Signal Monitor DC Value Channel A (Register 0x10D and

Register 0x10E)

Register 0x10D, Bits[7:0]—Channel A DC Value[7:0]

Register 0x10E, Bits[7:0]—Channel A DC Value[13:8]

These read-only registers hold the latest dc offset value computed

by the signal monitor for Channel A.

Signal Monitor DC Value Channel B (Register 0x10F and

Register 0x110)

Register 0x10F Bits[7:0]—Channel B DC Value[7:0]

Register 0x110 Bits[7:0]—Channel B DC Value[13:8]

These read-only registers hold the latest dc offset value computed

by the signal monitor for Channel B.

Signal Monitor SPORT Control (Register 0x111)

Bit 7—Reserved

Bit 6—RMS/MS Magnitude Output Enable

These bits enable the 20-bit rms or ms magnitude measurement

as output on the SPORT.

Bit 5—Peak Power Output Enable

Bit 5 enables the 13-bit peak measurement as output on

the SPORT.

Bit 4—Threshold Crossing Output Enable

Bit 4 enables the 13-bit threshold measurement as output on

the SPORT.

Bits[3:2]—SPORT SMI SCLK Divide

The values of these bits set the SPORT SMI SCLK divide ratio

from the input clock. A value of 0x01 sets divide by 2 (default),

a value of 0x10 sets divide by 4, and a value of 0x11 sets divide by 8.

Bit 1— SPORT SMI SCLK Sleep

Setting Bit 1 high causes the SMI SCLK to remain low when the

signal monitor block has no data to transfer.

Bit 0—Signal Monitor SPORT Output Enable

When set, Bit 0 enables the SPORT output of the signal monitor

to begin shifting out the result data from the signal monitor block.

Signal Monitor Control (Register 0x112)

Bit 7—Complex Power Calculation Mode Enable

This mode assumes I data is present on one channel and Q data

is present on the opposite channel. The result reported is the

complex power, measured as

2

Q

I +

Bits[6:4]—Reserved

Bit 3—Signal Monitor RMS/MS Select

Setting Bit 3 low selects rms power measurement mode. Setting

Bit 3 high selects ms power measurement mode.

Bits[2:1]—Signal Monitor Mode

Bit 2 and Bit 1 set the mode of the signal monitor for data output

to Register 0x116 to Register 0x11B. Setting Bit 2 and Bit 1 to

0x00 selects rms/ms power output; setting these bits to 0x01

selects peak power output; and setting 0x10 or 0x11 selects

threshold crossing output.

Bit 0—Signal Monitor Enable

Setting Bit 0 high enables the signal monitor block.

Signal Monitor Period (Register 0x113 to Register 0x115)

Register 0x113, Bits[7:0]—Signal Monitor Period[7:0]

Register 0x114, Bits[7:0]—Signal Monitor Period[15:8]

Register 0x115, Bits[7:0]—Signal Monitor Period[23:16]

This 24-bit value sets the number of clock cycles over which the

signal monitor performs its operation. Although this register

defaults to 64 (0x40), the minimum value for this register is 128

(0x80) cycles – writing values less than 128 can cause inaccurate

results.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27467E19B11SA | CONN PLUG 11POS STRAIGHT W/SCKT |

| IDT72805LB10PF8 | IC FIFO SYNC DUAL 256X18 128TQFP |

| VI-J4B-MX-S | CONVERTER MOD DC/DC 95V 75W |

| VI-25D-MX-F2 | CONVERTER MOD DC/DC 85V 75W |

| LTC1350IG#TRPBF | IC TXRX 3.3V EIA/TIA-562 28-SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9640ABCPZ-125 | 功能描述:IC ADC 14BIT 125MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 位数:12 采样率(每秒):1.8M 数据接口:并联 转换器数目:1 功率耗散(最大):1.82W 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:管件 输入数目和类型:2 个单端,单极 |

| AD9640ABCPZ-150 | 功能描述:模数转换器 - ADC 14Bit 150Msps Dual 1.8V PB Free ADC RoHS:否 制造商:Analog Devices 通道数量: 结构: 转换速率: 分辨率: 输入类型: 信噪比: 接口类型: 工作电源电压: 最大工作温度: 安装风格: 封装 / 箱体: |

| AD9640ABCPZ-80 | 功能描述:IC ADC 14BIT 80MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD9640ABCPZRL7-105 | 功能描述:模数转换器 - ADC 14Bit 105Msps Dual 1.8V PB Free ADC RoHS:否 制造商:Analog Devices 通道数量: 结构: 转换速率: 分辨率: 输入类型: 信噪比: 接口类型: 工作电源电压: 最大工作温度: 安装风格: 封装 / 箱体: |

| AD9640ABCPZRL7-125 | 功能描述:14 Bit Analog to Digital Converter 2 Input 2 Pipelined 64-LFCSP-VQ (9x9) 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:在售 位数:14 采样率(每秒):125M 输入数:2 输入类型:差分,单端 数据接口:并联 配置:S/H-ADC 无线电 - S/H:ADC:1:1 A/D 转换器数:2 架构:管线 参考类型:外部, 内部 电压 - 电源,模拟:1.7 V ~ 1.9 V 电压 - 电源,数字:1.7 V ~ 1.9 V 特性:同步采样 工作温度:-40°C ~ 85°C 封装/外壳:64-VFQFN 裸露焊盘,CSP 供应商器件封装:64-LFCSP-VQ(9x9) 标准包装:750 |

发布紧急采购,3分钟左右您将得到回复。