- 您现在的位置:买卖IC网 > PDF目录16426 > AD9880/PCBZ (Analog Devices Inc)KIT EVALUATION AD9880 PDF资料下载

参数资料

| 型号: | AD9880/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 38/64页 |

| 文件大小: | 0K |

| 描述: | KIT EVALUATION AD9880 |

| 标准包装: | 1 |

| 系列: | Advantiv® |

| 主要目的: | 视频,视频处理 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD9880 |

| 主要属性: | 模拟和 HDMI/DVI 双路显示器端口 |

| 次要属性: | 自动偏移,色域转换器,RGB 和 YCbCr 输出格式 |

| 已供物品: | 板 |

| 相关产品: | AD9880KSTZ-150-ND - IC INTERFACE/HDMI 150MHZ 100LQFP AD9880KSTZ-100-ND - IC INTERFACE/HDMI 100MHZ 100LQFP |

| 其它名称: | Q5281026 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

AD9880

Rev. 0 | Page 43 of 64

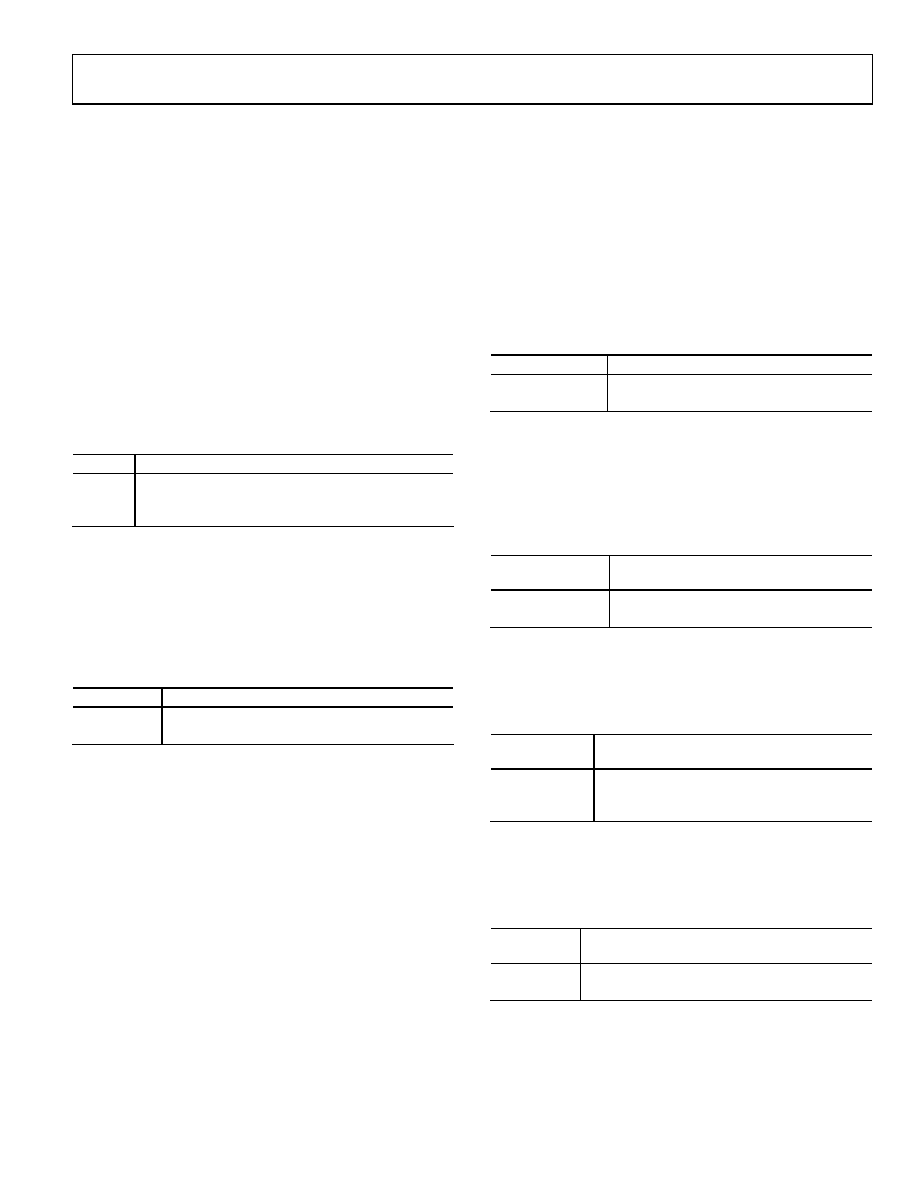

0x20

7-0

Sync Filter Window Width

This 8-bit register sets the distance in 40 MHz clock

periods (25 ns), which is the allowed distance for

Hsync pulses before and after the expected Hsync

edge. This is the heart of the filter in that it only looks

for Hsync pulses at a given time (plus or minus this

window) and then ignores extraneous equalization

pulses that disrupt accurate PLL operation. The

power-up default setting is 10d, or 200 ns on either

side of the expected Hsync.

0x21

7

Sync Processing Filter Enable

This bit selects which Hsync is used for the sync

processing functions of internal Coast, H/V count,

field detection, and Vsync duration counts. A clean

Hsync is fundamental to accurate processing of the

sync. The power-up default setting is 1.

Table 35. Sync Processing Filter Enable

Select

Result

0

Sync processing uses raw Hsync or SOG

1

Sync processing uses regenerated Hsync from sync

filter

0x21

6

PLL Sync Filter Enable

This bit selects which signal the PLL uses. It can select

between raw Hsync or SOG, or filtered versions. The

filtering of the Hsync and SOG can eliminate nearly

all extraneous transitions which have traditionally

caused PLL disruption. The power-up default setting

is 0.

Table 36. PLL Sync Filter Enable

Select

Result

0

PLL uses raw Hsync or SOG inputs

1

PLL uses filtered Hsync or SOG inputs

0x21

5

Vsync Filter Enable

The purpose of the Vsync filter is to guarantee the

position of the Vsync edge with respect to the Hsync

edge and to generate a field signal. The filter works by

examining the placement of Vsync and regenerating a

correctly placed Vsync one line later. The Vsync is

first checked to see whether it occurs in the Field 0

position or the Field 1 position. This is done by

checking the leading edge position against the sync

separator threshold and the Hsync position. The

Hsync width is divided into four quadrants with

Quadrant 1 starting at the Hsync leading edge plus a

sync separator threshold. If the Vsync leading edge

occurs in Quadrant 1 or 4 then the field is set to 0 and

the output Vsync is placed coincident with the Hsync

leading edge. If the Vsync leading edge occurs in

Quadrant 2 or 3 then the field is set to 1 and the

output Vsync leading edge is placed in the center of

the line. In this way, the Vsync filter creates a

predictable relative position between Hsync and

Vsync edges at the output.

If the Vsync occurs near the Hsync edge, this guaran-

tees that the Vsync edge follows the Hsync edge. This

performs filtering also in that it requires a minimum

of 64 lines between Vsyncs. The Vsync filter cleans up

extraneous pulses that might occur on the Vsync. This

should be enabled whenever the Hsync/Vsync count is

used. Setting this bit to 0 disables the Vsync filter.

Setting this bit to 1 enables the Vsync filter. Power-up

default is 0.

Table 37. Vsync Filter Enable

Vsync Filter Bit

Result

0

Vsync filter disabled

1

Vsync filter enabled

0x21

4

Vsync Duration Enable

This enables the Vsync duration block which is

designed to be used with the Vsync filter. Setting the

bit to 0 leaves the Vsync output duration unchanged;

setting the bit to 1 sets the Vsync output duration

based on Register 0x22. The power-up default is 0.

Table 38. Vsync Duration Enable

Vsync

Duration Bit

Result

0

Vsync output duration unchanged

1

Vsync output duration set by 0x22

0x21

3

Auto Offset Clamp Mode

This bit specifies if the auto offset measurement takes

place during clamp or either 10 or 16 clocks afterward.

The measurement takes 6 clock cycles.

Table 39. AO Clamp Mode

AO

Offset Mode

Result

0

Auto offset measurement takes place during

clamp period

1

Auto offset measurement is set by 0x21, Bit 2

0x21

2

Auto Offset Clamp Length

This bit sets the delay following the end of the clamp

period for AO measurement. This bit is valid only if

Register 0x21, Bit 3 = 1.

Table 40. AO Clamp Length

AO Offset

Clamp Bit

Result

0

Delay is 10 clock cycles

1

Delay is 16 clock cycles

0x22

7-0

Vsync Duration

This is used to set the output duration of the Vsync,

and is designed to be used with the Vsync filter. This

is valid only if Register 0x21, Bit 4 is set to 1. Power-up

default is 4.

相关PDF资料 |

PDF描述 |

|---|---|

| S01-02-R | SOLDER SLEEVE IMMERS RESIS .650" |

| ILSB1206ER180K | INDUCTOR 18UH 10% 1206 |

| 242489-000 | CWT-3811 |

| VI-J10-EX | CONVERTER MOD DC/DC 5V 75W |

| GEC20DRYH-S734 | CONN EDGECARD 40POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9880XSTZ-100 | 制造商:Analog Devices 功能描述:IC, ANALOG/HDMI DUAL DISPLAY INTERFACE, PQFP100 |

| AD9882 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Interface for Flat Panel Displays |

| AD9882/PCB | 制造商:Analog Devices 功能描述:DUAL INTRFC FOR FLAT PNL DISPLAY 100LQFP - Bulk |

| AD9882A | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Interface for Flat Panel Displays |

| AD9882A/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual Interface for Flat Panel Displays |

发布紧急采购,3分钟左右您将得到回复。