- 您现在的位置:买卖IC网 > PDF目录1895 > ADAU1373BCBZ-RL (Analog Devices Inc)IC CODEC LP CLASS G HP 81WLCSP PDF资料下载

参数资料

| 型号: | ADAU1373BCBZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 251/296页 |

| 文件大小: | 0K |

| 描述: | IC CODEC LP CLASS G HP 81WLCSP |

| 标准包装: | 3,000 |

| 类型: | 音频编解码器 |

| 数据接口: | I²C,串行 |

| 分辨率(位): | 24 b |

| ADC / DAC 数量: | 1 / 2 |

| 三角积分调变: | 是 |

| S/N 比,标准 ADC / DAC (db): | 96 / 96 |

| 动态范围,标准 ADC / DAC (db): | 96 / 96 |

| 电压 - 电源,模拟: | 1.62 V ~ 1.98 V |

| 电压 - 电源,数字: | 1.08 V ~ 1.98 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 81-UFBGA,WLCSP |

| 供应商设备封装: | 81-WLCSP(4.05x3.82) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页第226页第227页第228页第229页第230页第231页第232页第233页第234页第235页第236页第237页第238页第239页第240页第241页第242页第243页第244页第245页第246页第247页第248页第249页第250页当前第251页第252页第253页第254页第255页第256页第257页第258页第259页第260页第261页第262页第263页第264页第265页第266页第267页第268页第269页第270页第271页第272页第273页第274页第275页第276页第277页第278页第279页第280页第281页第282页第283页第284页第285页第286页第287页第288页第289页第290页第291页第292页第293页第294页第295页第296页

ADAU1373

Rev. 0 | Page 58 of 296

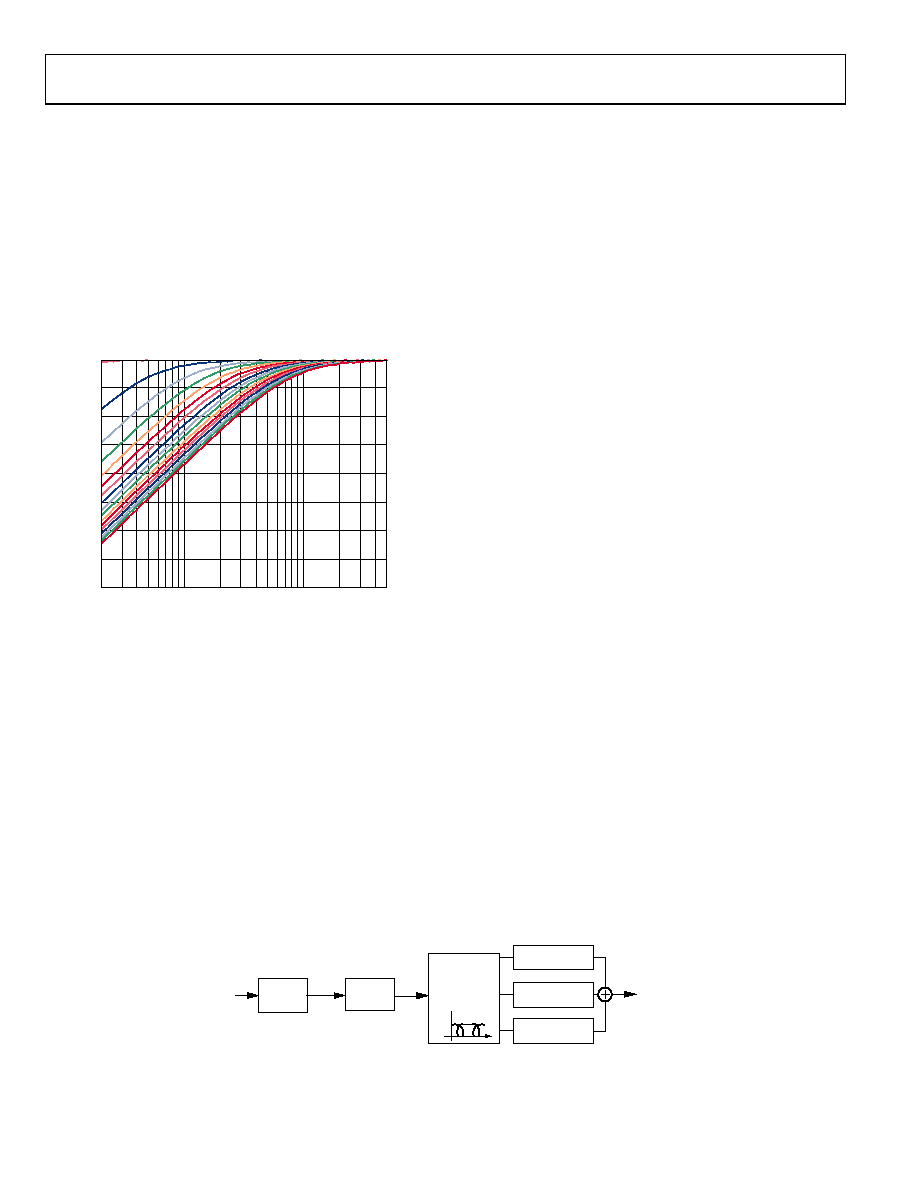

Post-HPFs

The post-HPF cutoff frequency is selectable via Register 0x7D,

Bits[7:3] as 3.7 Hz for dc removal or from 50 Hz up to 800 Hz,

with a 50 Hz step for low frequency component filtering. This

HPF block can be enabled or disabled for the left or right channel,

controlled by Register 0x7D, Bits[1:0]. The HPF calculates the

dc value of the signal, which is subtracted from the signal when

enabled. When the HPF block is disabled, Bit 2 of Register 0x7D

determines whether the calculated dc value is maintained and

subtracted from the input signal or cleared to 0.

Figure 105 shows the post-HPF frequency response plots for

various cutoff frequency settings.

–40

0

–35

–30

–25

–20

–15

–10

–5

MAG

N

IT

U

DE

(

d

BF

S

)

20

5k

100

1k

FREQUENCY (Hz)

08975-

038

Figure 105. Post-HPF Frequency Response

DYNAMIC RANGE CONTROL (DRC)

The DRC is used to control the dynamic range of the signal.

It provides the capability to match the dynamic range of the

incoming signal with the dynamic range of the signal fed to the

next block or device without losing the signal-to-noise ratio.

The ADAU1373 provides three full-band DRCs or one multiband

DRC (MDRC). However, at any given time, either the three full-

band DRCs or the MDRC can be used. Register 0x80 through

Register 0xB2 are used for setting the MDRC or full-band DRCs.

The MDRC and the seven-band EQ share the same register

addresses (Register 0x80 through Register 0xBD). Therefore, for

the MDRC, ensure that the EQ coefficient writing enable bit

(EQ_WR_EN, Bit 0 in Register 0xBE) = 0; whereas for the

seven-band EQ, the EQ_WR_EN bit = 1.

MDRC

The MDRC provides a multiband dynamic range control by split-

ting the signal into three bands, depending on the frequency: low,

mid, and high. Each of the bands is processed separately, and

individual controls are provided for each band DRC. The MDRC

can be enabled or disabled by the MDRC_EN bit (Register 0xB2,

Bit 0) (see the MDRC block diagram in Figure 106).

The 3-band MDRC is composed of a second-order high-pass

IIR filter, a second-order low-pass IIR filter, the frequency

splitter, and three individual DRCs for low, mid, and high bands.

The 3 dB cutoff frequency of the HPF can be set from 50 Hz to

800 Hz in 50 Hz steps, configured using the MDRC_HPF bits

(Register 0xB0, Bits[5:2]).

The LPF cutoff frequency can be set to 4 kHz, 8 kHz, or 20 kHz

via the MDRC_LPF bits (Register 0xB0, Bits[1:0]).

The HPF and LFP can be enabled or disabled by using the

MDRC_LPFEN and MDRC_HPFEN bits in Register 0xB2.

The crossover frequencies between the low band and high band

are defined in Register 0xB1 by the MDRC_CROSS_LOW bits

(Bits[3:0]) and the MDRC_CROSS_HIGH bits (Bits[7:4]). The

crossover frequency between low band and mid band can be

varied from 100 Hz to 1600 Hz in steps of 100 Hz. The crossover

frequency for the mid-to-high bands can be varied from 1 kHz

to 16 kHz in steps of 1 kHz.

All of the previous frequency values are based on a 48 kHz

sampling rate. If the input signals are of a different sampling rate,

the values should be scaled accordingly.

Using the DRC

The ADAU1373 provides three DRCs that can be used as full band.

The DRCs are shared between full-band DRC or MDRC. When

the full-band DRCs are in use, the MDRC is not available. For full-

band DRC, the crossover filters can be disabled in Register 0xB2

via the MDRC_HPFEN bit (Bit 1) and the MDRC_LPFEN bit

(Bit 2). Each of the three DRCs has its own registers: Register 0x80

to Register 0x8F for DRC1, Register 0x90 to Register 0x9F for

DRC2, and Register 0xA0 to Register 0xAF for DRC3, plus enable

or disable bits, which are set by the DRCEN bits (Bits[1:0]) in

Register 0x8D, Register 0x9D, and Register 0xAD.

FREQUENCY

SPLITTER

f

HPF

LPF

|H(f)|

4kHz/

8kHz/20kHz

50Hz TO 800Hz

(50Hz STEP)

DRC

LOW BAND

DRC

MID BAND

DRC

HIGH BAND

0897

5-

039

Figure 106. MDRC Block Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| ADAU1381BCPZ | IC AUDIO CODEC STEREO LN 32LFCSP |

| ADAU1761BCPZ-RL | IC SIGMADSP CODEC PLL 32LFCSP |

| ADAU1781BCPZ-RL7 | IC SIGMADSP CODEC LN 32LFCSP |

| ADAU1961WBCPZ-R7 | IC STEREO AUD CODEC LP 32LFCSP |

| ADAU1966WBSTZ | IC DAC 24BIT SPI/I2C 192K 80LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAU1381 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Noise Stereo Codec with Enhanced Recording and Playback Processing |

| ADAU1381BCBZ-RL | 功能描述:IC AUDIO CODEC STEREO LN 30WLCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADAU1381BCBZ-RL7 | 功能描述:IC AUDIO CODEC STEREO LN 30WLCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADAU1381BCPZ | 功能描述:IC AUDIO CODEC STEREO LN 32LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADAU1381BCPZ-RL | 功能描述:IC AUDIO CODEC STEREO LN 32LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。