- 您现在的位置:买卖IC网 > PDF目录1989 > ADF4350BCPZ-RL (Analog Devices Inc)IC SYNTH PLL VCO FN/IN 32LFCSP PDF资料下载

参数资料

| 型号: | ADF4350BCPZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 27/32页 |

| 文件大小: | 0K |

| 描述: | IC SYNTH PLL VCO FN/IN 32LFCSP |

| 产品变化通告: | ADF4350, ADF4905/6 N-counter Change 05/Mar/2012 |

| 设计资源: | Broadband Low EVM Direct Conversion Transmitter (CN0134) Broadband Low EVM Direct Conversion Transmitter Using LO Divide-by-2 Modulator (CN0144) Using low noise linear drop-out regulators to power wideband PLL & VCO IC's (CN0147) |

| 标准包装: | 5,000 |

| 类型: | 扇出配送,分数-N,整数-N,时钟/频率合成器(RF) |

| PLL: | 是 |

| 输入: | CMOS,TTL |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:3 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 4.4GHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页

ADF4350

Rev. A | Page 4 of 32

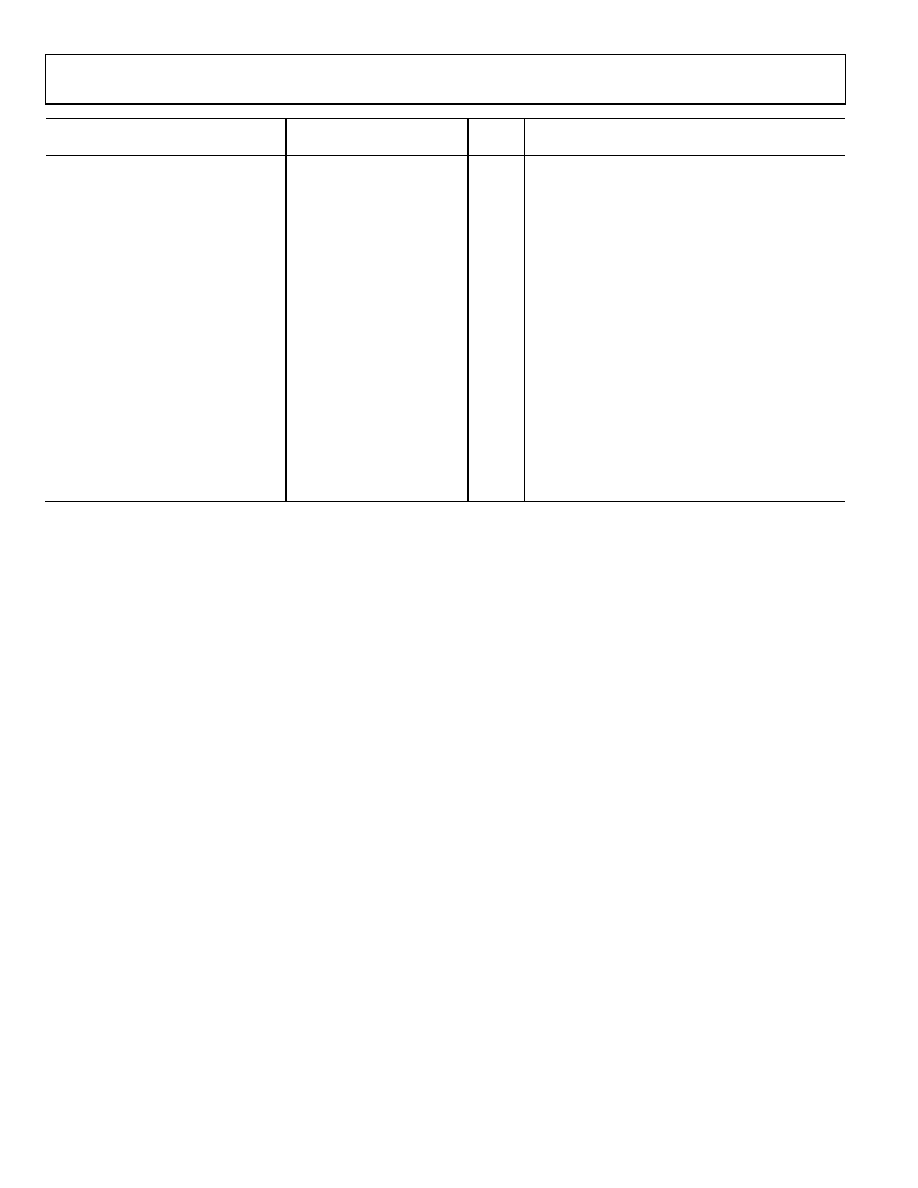

B Version

Parameter

Min

Typ

Max

Unit

Conditions/Comments

NOISE CHARACTERISTICS

VCO Phase-Noise Performance6

89

dBc/Hz

10 kHz offset from 2.2 GHz carrier

114

dBc/Hz

100 kHz offset from 2.2 GHz carrier

134

dBc/Hz

1 MHz offset from 2.2 GHz carrier

148

dBc/Hz

5 MHz offset from 2.2 GHz carrier

86

dBc/Hz

10 kHz offset from 3.3 GHz carrier

111

dBc/Hz

100 kHz offset from 3.3 GHz carrier

134

dBc/Hz

1 MHz offset from 3.3 GHz carrier

145

dBc/Hz

5 MHz offset from 3.3 GHz carrier

83

dBc/Hz

10 kHz offset from 4.4 GHz carrier

110

dBc/Hz

100 kHz offset from 4.4 GHz carrier

132

dBc/Hz

1 MHz offset from 4.4 GHz carrier

145

dBc/Hz

5 MHz offset from 4.4 GHz carrier

Normalized Phase Noise Floor

(PNSYNTH)7

220

dBc/Hz

PLL Loop BW = 500 kHz

Normalized 1/f Noise (PN1_f)8

111

dBc/Hz

10 kHz offset; normalized to 1 GHz

In-Band Phase Noise9

97

dBc/Hz

3 kHz offset from 2113.5 MHz carrier

Integrated RMS Jitter10

0.5

ps

Spurious Signals Due to PFD Frequency

70

dBc

Level of Signal With RF Mute Enabled

40

dBm

1 AC coupling ensures AVDD/2 bias.

2 Guaranteed by design. Sample tested to ensure compliance.

3 ICP is internally modified to maintain constant loop gain over the frequency range.

4 TA = 25°C; AVDD = DVDD = VVCO = 3.3 V; prescaler = 8/9; fREFIN = 100 MHz; fPFD = 25 MHz; fRF = 4.4 GHz.

5 Using 50 Ω resistors to VVCO, into a 50 Ω load. Power measured with auxiliary RF output disabled. The current consumption of the auxiliary output is the same as for the

main output.

6 The noise of the VCO is measured in open-loop conditions.

7 The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20 log N (where N is the N divider

value) and 10 log FPFD. PNSYNTH = PNTOT 10 log FPFD 20 log N.

8 The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency, fRF,

and at a frequency offset f is given by PN = P1_f + 10log(10 kHz/f) + 20log(fRF/1 GHz). Both the normalized phase noise floor and flicker noise are modeled in ADIsimPLL.

9 fREFIN = 100 MHz; fPFD = 25 MHz; offset frequency = 10 kHz; VCO frequency = 4227 MHz, output divide by two enabled. RFOUT = 2113.5 MHz; N = 169; loop BW = 40 kHz,

ICP = 313 μA; low noise mode. The noise was measured with an EVAL-ADF4350EB1Z and the Agilent E5052A signal source analyzer.

10 fREFIN = 100 MHz; fPFD = 25 MHz; VCO frequency = 4400 MHz, RFOUT = 4400 MHz; N = 176; loop BW = 40 kHz, ICP = 313 μA; low noise mode. The noise was measured with

an EVAL-ADF4350EB1Z and the Agilent E5052A signal source analyzer.

相关PDF资料 |

PDF描述 |

|---|---|

| ADF4351BCPZ | IC SYNTH PLL VCO 32LFCSP |

| ADF4360-0BCPZRL7 | IC SYNTHESIZER VCO 24LFCSP |

| ADF4360-1BCPZRL7 | IC SYNTHESIZER VCO 24LFCSP |

| ADF4360-2BCPZRL7 | IC SYNTHESIZER VCO 24LFCSP |

| ADF4360-3BCPZRL7 | IC SYNTHESIZER VCO 24LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADF4350BCPZ-RL7 | 功能描述:IC SYNTH PLL VCO FN/IN 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ADF4350BCPZ-U6 | 制造商:Analog Devices 功能描述: |

| ADF4350EB1Z | 制造商:Analog Devices 功能描述:AD EVAL BOARD - Bulk |

| ADF4351 | 制造商:AD 制造商全称:Analog Devices 功能描述:Wideband Synthesizer |

| ADF4351BCPZ | 功能描述:IC SYNTH PLL VCO 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。