- 您现在的位置:买卖IC网 > PDF目录9659 > ADN2812ACPZ-RL (Analog Devices Inc)IC CLOCK/DATA RECOVERY 32LFCSP PDF资料下载

参数资料

| 型号: | ADN2812ACPZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/28页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 32LFCSP |

| 标准包装: | 5,000 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH |

| 输入: | CML |

| 输出: | CML |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 2.7GHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

Data Sheet

ADN2812

Rev. E | Page 19 of 28

The two uses of the reference clock are mutually exclusive. The

reference clock can be used either as an acquisition aid for the

ADN2812 to lock onto data or to measure the frequency of the

incoming data to within 0.01%. (There is the capability to meas-

ure the data rate to approximately ±10% without the use of a

reference clock.) The modes are mutually exclusive because, in

the first use, the user knows the exact data rate and wants to

force the part to lock onto only that data rate; in the second use,

the user does not know the data rate and wants to measure it.

Lock to reference mode is enabled by writing a 1 to I2C Register

Bit CTRLA[0]. Fine data rate readback mode is enabled by

writing a 1 to I2C Register Bit CTRLA[1]. Writing a 1 to both

of these bits at the same time causes an indeterminate state

and is not supported.

Using the Reference Clock to Lock onto Data

Writing CTRLA[0] = 1 puts the ADN2812 into lock-to-REFCLK

(LTR) mode. In this mode, the ADN2812 locks onto a fre-

quency derived from the reference clock according to the

following equation:

Data Rate/2CTRLA[5:2] = REFCLK/2CTRLA[7:6]

The user must know exactly what the data rate is and provide

a reference clock that is a function of this rate. The ADN2812

can still be used as a continuous rate device in this configu-

ration, provided that the user has the ability to provide a

reference clock that has a variable frequency (see the Appli-

cation Note AN-632).

The reference clock can be anywhere between 12.3 MHz and

200 MHz. By default, the ADN2812 expects a reference clock

between 12.3 MHz and 25 MHz. If it is between 25 MHz and

50 MHz, 50 MHz and 100 MHz, or 100 MHz and 200 MHz,

the user needs to configure the ADN2812 to use the correct

reference frequency range by setting two bits of the CTRLA

register, CTRLA[7:6].

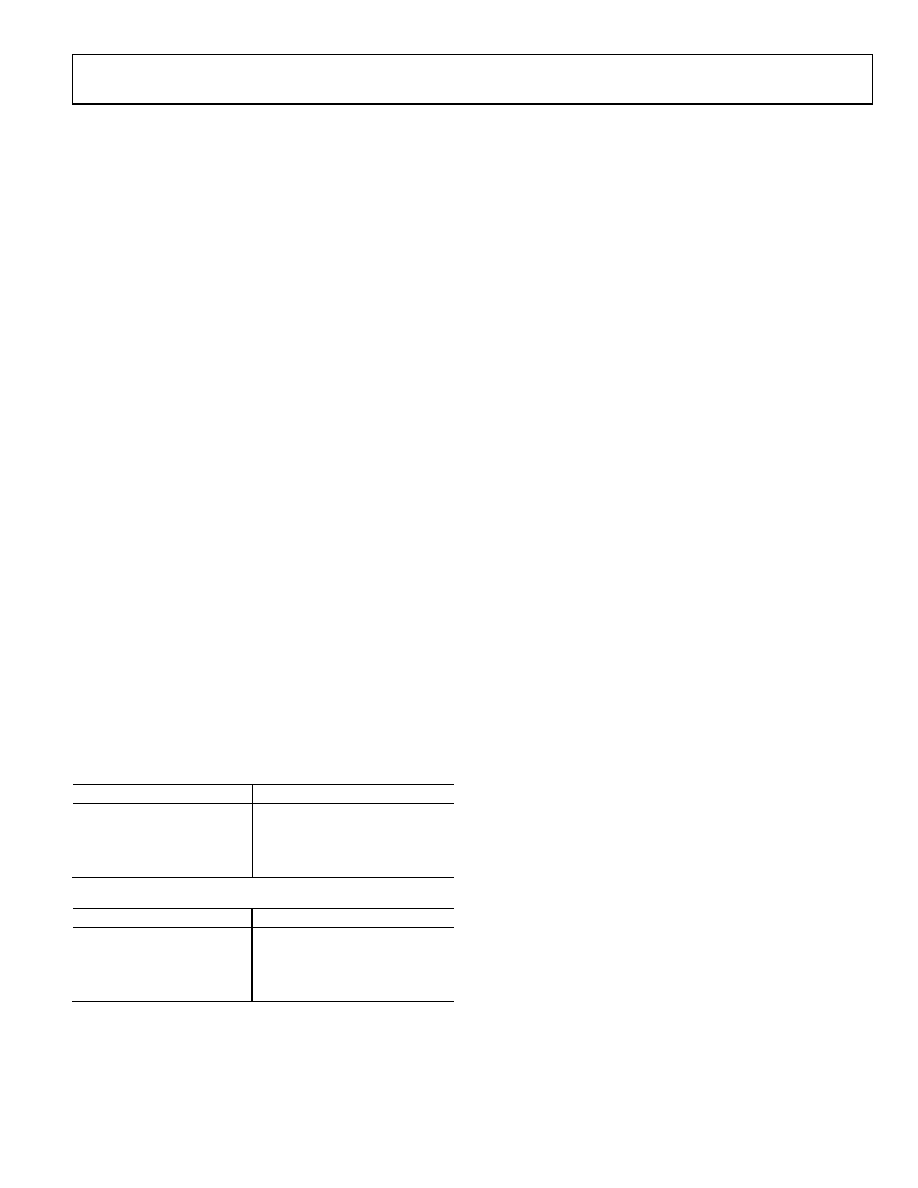

Table 11. CTRLA[7:6] Settings

CTRLA[7:6]

Range (MHz)

00

12.3 to 25

01

25 to 50

10

50 to 100

11

100 to 200

Table 12. CTRLA[5:2] Settings

CTRLA[5:2]

Ratio

0000

1

0001

2

n

2n

1000

256

The user can specify a fixed integer multiple of the reference

clock to lock onto using CTRLA[5:2], where CTRLA is set to

the data rate/DIV_FREF and where DIV_FREF represents the

divided-down reference referred to the 12.3 MHz to 25 MHz

band. For example, if the reference clock frequency is 38.88 MHz

and the input data rate is 622.08 Mb/s, CTRLA[7:6] is set to

[01] to give a divided-down reference clock of 19.44 MHz.

CTRLA[5:2] is set to [0101], that is, 5, because

622.08 Mb/s/19.44 MHz = 25

In this mode, if the ADN2812 loses lock for any reason, it

relocks onto the reference clock and continues to output a

stable clock.

While the ADN2812 is operating in LTR mode, if the user ever

changes the reference frequency (the FREF range, CTRLA[7:6] or

the FREF ratio, CTRLA[5:2]), this must be followed by writing a 1

to 0 transition into the CTRLB[5] bit to initiate a new frequency

acquisition.

A frequency acquisition can also be initiated in LTR mode

by writing a 0 to 1 transition into CTRLA[0]; however, it is

recommended that a frequency acquisition be initiated by

writing a 1 to 0 transition into CTRLB[5] as previously

explained.

Using the Reference Clock to Measure Data Frequency

The user can also provide a reference clock to measure the

recovered data frequency, in which case the ADN2812 compares

the frequency of the incoming data to the incoming reference

clock and returns a ratio of the two frequencies to 0.01%

(100 ppm). The accuracy error of the reference clock is added

to the accuracy of the ADN2812 data rate measurement. For

example, if a 100 ppm accuracy reference clock is used, the total

accuracy of the measurement is within 200 ppm.

The reference clock can range from 12.3 MHz to 200 MHz.

The ADN2812 expects a reference clock between 12.3 MHz

and 25 MHz by default. If it is between 25 MHz and 50 MHz,

50 MHz and 100 MHz, or 100 MHz and 200 MHz, the user

needs to configure the ADN2812 to use the correct reference

frequency range by setting two bits of the CTRLA register,

CTRLA[7:6]. Using the reference clock to determine the

frequency of the incoming data does not affect the manner

in which the part locks onto data. In this mode, the reference

clock is used only to determine the frequency of the data. For

this reason, the user does not need to know the data rate to use

the reference clock in this manner.

相关PDF资料 |

PDF描述 |

|---|---|

| ADN2819ACPZ-CML-RL | IC CLOCK/DATA RECOVERY 48LFCSP |

| MS27484T24B35SC | CONN PLUG 128POS STRAIGHT W/SCKT |

| MS27484T24B35SB | CONN PLUG 128POS STRAIGHT W/SCKT |

| MS27473E24B35SB | CONN PLUG 128POS STRAIGHT W/SCKT |

| ADN2818ACPZ-RL7 | IC CLOCK/DATA RECOVERY 32-LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADN2812ACPZ-RL7 | 功能描述:IC CLOCK/DATA RECOVERY 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2813 | 制造商:AD 制造商全称:Analog Devices 功能描述:Continuous Rate 10 Mb/s to 1.25 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2813ACPZ | 功能描述:IC CLK/DATA REC 1.25GBPS 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| ADN2813ACPZ-500RL7 | 功能描述:IC CLK/DATA REC 1.25GBPS 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2813ACPZ-RL7 | 功能描述:IC CLK/DATA REC 1.25GBPS 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

发布紧急采购,3分钟左右您将得到回复。