- 您现在的位置:买卖IC网 > PDF目录9660 > ADN2818ACPZ-RL7 (Analog Devices Inc)IC CLOCK/DATA RECOVERY 32-LFCSP PDF资料下载

参数资料

| 型号: | ADN2818ACPZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 1/40页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 32-LFCSP |

| 标准包装: | 1,500 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH |

| 输入: | CML |

| 输出: | CML |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 2.7GHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 带卷 (TR) |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

Continuous Rate 10 Mbps to 2.7 Gbps Clock

and Data Recovery ICs

Data Sheet

Rev. E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibilityisassumedbyAnalogDevicesforitsuse,norforanyinfringementsofpatentsorother

rightsofthirdpartiesthatmayresultfromitsuse.Specificationssubjecttochangewithoutnotice.No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

2007–2013 Analog Devices, Inc. All rights reserved.

FEATURES

Serial data input: 10 Mbps to 2.7 Gbps

Exceeds ITU-T jitter specifications

Integrated limiting amplifier

5 mV p-p sensitivity (ADN2817 only)

Adjustable slice level: ±100 mV (ADN2817 only)

Patented dual-loop clock recovery architecture

Programmable LOS detect (ADN2817 only)

Integrated PRBS generator and detector

No reference clock required

Loss of lock indicator

Supports double data rate

Bit error rate monitor (BERMON) or sample phase adjust options

Rate selectivity without the use of a reference clock

I2C interface to access optional features

Single-supply operation: 3.3 V

Low power

650 mW (ADN2817)

600 mW (ADN2818)

5 mm × 5 mm 32-lead LFCSP

APPLICATIONS

SONET OC-1, OC-3, OC-12, OC-48, and all associated FEC rates

Fibre Channel, 2× Fibre Channel, GbE, HDTV

WDM transponders

Regenerators/repeaters

Test equipment

GENERAL DESCRIPTION

The ADN2817/ADN2818 provide the receiver functions of

quantization, signal level detect, and clock and data recovery for

continuous data rates from 10 Mbps to 2.7 Gbps. The ADN2817/

ADN2818 automatically lock to all data rates without the need for

an external reference clock or programming. All SONET jitter

requirements are exceeded, including jitter transfer, jitter generation,

and jitter tolerance. All specifications are quoted for 40°C to

+85°C ambient temperature, unless otherwise noted.

This device, together with a PIN diode and a TIA preamplifier,

can implement a highly integrated, low cost, and low power

fiber optic receiver.

The ADN2817/ADN2818 have many optional features available

through an I2C interface. For example, the user can read back

the data rate onto which the ADN2817 or ADN2818 is locked,

or the user can set the device to lock only to one particular data

rate if provisioning of data rates is required. A BERMON circuit

provides an estimate of the received bit error rate (BER) without

interruption of the data. Alternatively, the user can adjust the

data sampling phase to optimize the received BER.

The ADN2817/ADN2818 are available in a compact 5 mm ×

5 mm, 32-lead, lead frame chip scale package.

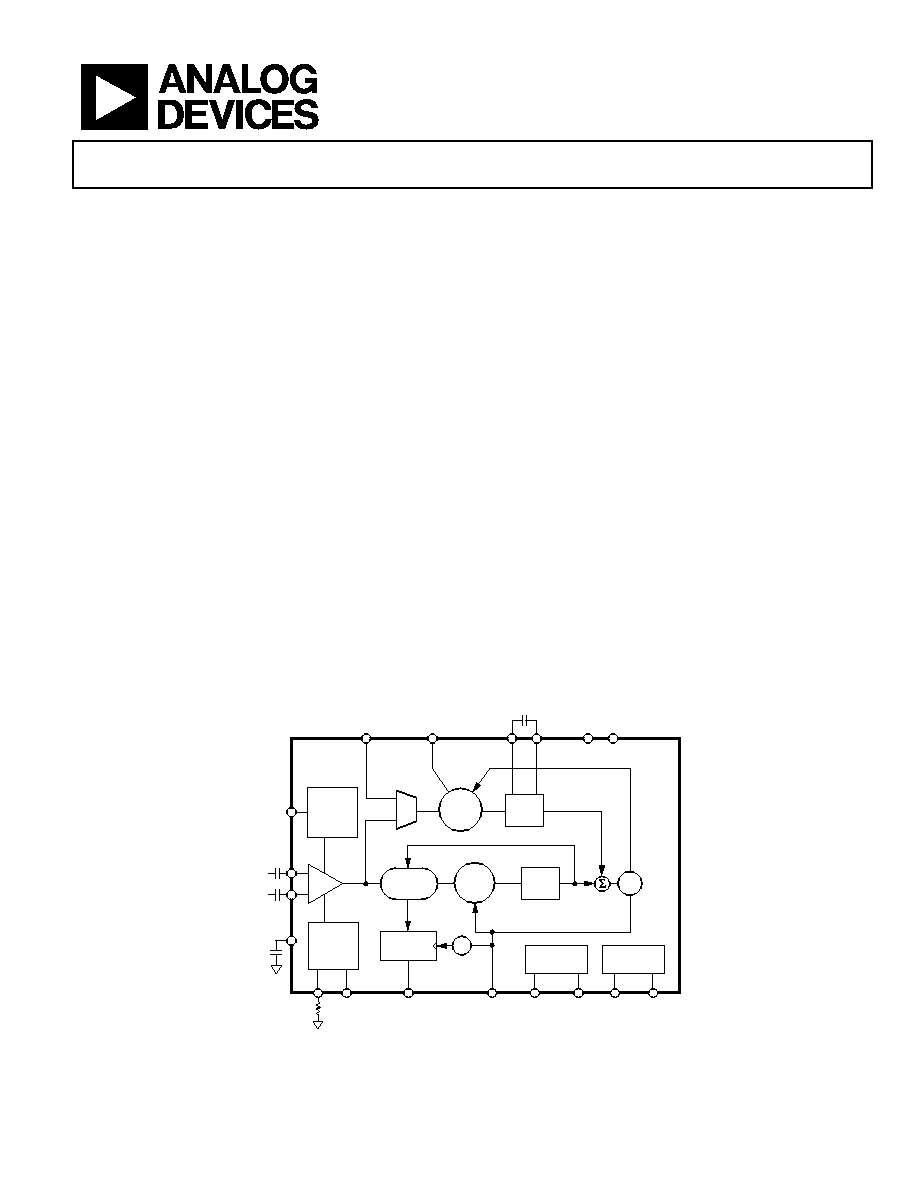

FUNCTIONAL BLOCK DIAGRAM

LOOP

FILTER

PHASE

DET

SLICE

ADJUST

(ADN2817

ONLY)

LOS

DETECT

(ADN2817

ONLY)

DATA

RETIMING

I2C

REGISTERS

LOOP

FILTER

FREQ/

LOCK

DET

VCC VEE

ADN2817/ADN2818

CF1

CF2

LOL

REFCLKP/REFCLKN

(OPTIONAL)

SLICEP/

SLICEN

PIN

NIN

VREF

THRADJ

LOS

DATAOUTP/

DATAOUTN

CLKOUTP/

CLKOUTN

SCK

SDA

VCO

06001-

001

BERMON

VBER

BERMODE

PHASE

SHIFTER

ΔФ

Figure 1.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27472E24B35SA | CONN RCPT 128POS WALL MNT W/SCKT |

| MS27468T25B19P | CONN RCPT 19POS JAM NUT W/PINS |

| SY87701LZG | IC CLOCK/DATA RECOVERY 28-SOIC |

| VI-21Z-MV-F2 | CONVERTER MOD DC/DC 2V 60W |

| SY87721LHY TR | IC CLOCK/DATA RECOVERY 64-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADN2819 | 制造商:AD 制造商全称:Analog Devices 功能描述:Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2819ACP-CML | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP Tray 制造商:Rochester Electronics LLC 功能描述:MULTI-RATE 2.7GBPS CDR/ PA LOW POWER I.C - Bulk |

| ADN2819ACP-CML-RL | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP T/R |

| ADN2819ACPZ-CML | 功能描述:IC CLOCK/DATA RECOVERY 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2819ACPZ-CML1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

发布紧急采购,3分钟左右您将得到回复。