- 您现在的位置:买卖IC网 > PDF目录9660 > ADN2818ACPZ-RL7 (Analog Devices Inc)IC CLOCK/DATA RECOVERY 32-LFCSP PDF资料下载

参数资料

| 型号: | ADN2818ACPZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/40页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 32-LFCSP |

| 标准包装: | 1,500 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH |

| 输入: | CML |

| 输出: | CML |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 2.7GHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

ADN2817/ADN2818

Data Sheet

Rev. E | Page 16 of 40

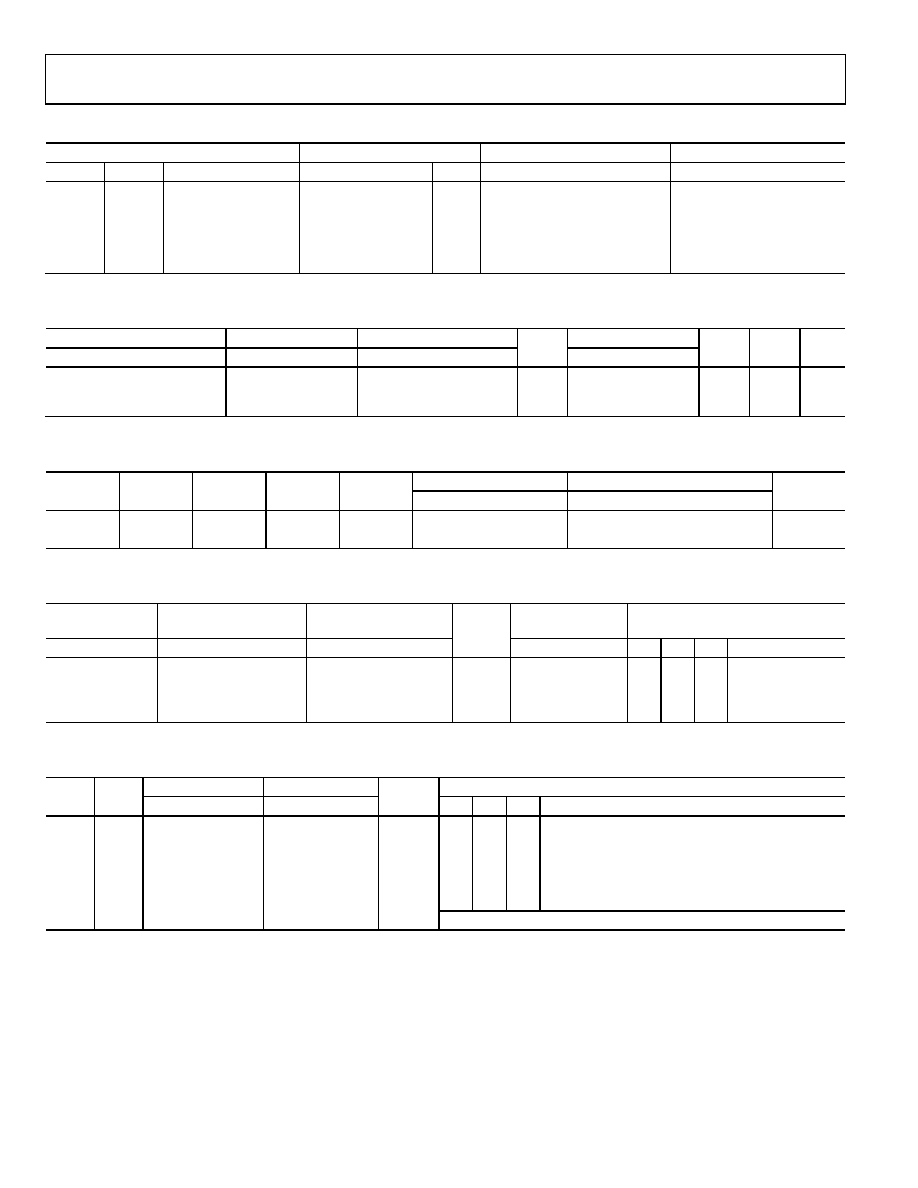

Table 10. Control Register, CTRLA

fREF Range

Data Rate/DIV_FREF Ratio

Measure Data Rate

Lock to REFCLK

D7

D6

Range

D5

D4

D3

D2

Ratio

D1

D0

Set to 0

10 MHz to 25 MHz

0

1

Set to 1 to measure data rate

0 = lock to input data

Set to 0

Set to 1

25 MHz to 50 MHz

0

1

2

1 = lock to reference clock

Set to 1

Set to 0

50 MHz to 100 MHz

0

1

0

4

Set to 1

100 MHz to 200 MHz

n

2n

1

0

256

Table 11. Control Register, CTRLB

Config LOL

Reset MISC[4]

Initiate Freq Acquisition

Reset MISC[2]

D7

D6

D5

D4

D3

D2

D1

D0

0 = LOL pin normal

operation

1 = LOL pin is static LOL

Write a 1 followed

by 0 to reset MISC[4]

Write a 1 followed

by 0 to initiate a

frequency acquisition

Set

to 0

Write a 1 followed

by 0 to reset MISC[2]

Set

to 0

Set

to 0

Set

to 0

Table 12. Control Register, CTRLC

Configure LOS

Squelch Mode

D7

D6

D5

D4

D3

D2

D1

D0

Set to 0

0 = active high LOS

0 = squelch CLK and DATA

Set to 0

1 = active low LOS

1 = squelch CLK or DATA

Table 13. Control Register, CTRLD

CDR Bypass

Disable

DATAOUT Buffer

Disable

CLKOUT Buffer

Initiate PRBS

Sequence

PRBS Mode

D7

D6

D5

D4

D3

D2

D1

D0

Function

0 = CDR enabled

0 = data buffer enabled

0 = CLK buffer enabled

Set to 0

Write a 1 followed

by 0 to initiate a

PRBS generate

sequence

0

Power-down PRBS

1 = CDR disabled

1 = data buffer disabled

1 = CLK buffer disabled

0

1

Generate mode

1

0

Detect mode

Table 14. Control Registers, CTRLE/BERCTLB

Enable BERMON

BER Stdby Mode

PRBS/DDR Enable and Output Mode

D7

D6

D5

D4

D3

D2

D1

D0

Function

Set

to 0

Set

to 0

1 = BERMON

enabled

0 = BERMON

disabled

1 = place BERMON

in low power

standby mode

0 = BERMON

ready

Set to 0

0

Normal data rate output mode

0

1

Offset decision circuit (ODC) output mode1

0

1

0

Enable DDR mode (double data rate mode)

0

1

Offset decision circuit (ODC) output in DDR mode1

1

0

1

Enable PRBS detector/generator

All other combinations reserved

1

See AN-941 Application Note, BER Monitor User Guide.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27472E24B35SA | CONN RCPT 128POS WALL MNT W/SCKT |

| MS27468T25B19P | CONN RCPT 19POS JAM NUT W/PINS |

| SY87701LZG | IC CLOCK/DATA RECOVERY 28-SOIC |

| VI-21Z-MV-F2 | CONVERTER MOD DC/DC 2V 60W |

| SY87721LHY TR | IC CLOCK/DATA RECOVERY 64-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADN2819 | 制造商:AD 制造商全称:Analog Devices 功能描述:Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2819ACP-CML | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP Tray 制造商:Rochester Electronics LLC 功能描述:MULTI-RATE 2.7GBPS CDR/ PA LOW POWER I.C - Bulk |

| ADN2819ACP-CML-RL | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP T/R |

| ADN2819ACPZ-CML | 功能描述:IC CLOCK/DATA RECOVERY 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2819ACPZ-CML1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

发布紧急采购,3分钟左右您将得到回复。