- 您现在的位置:买卖IC网 > PDF目录9660 > ADN2818ACPZ-RL7 (Analog Devices Inc)IC CLOCK/DATA RECOVERY 32-LFCSP PDF资料下载

参数资料

| 型号: | ADN2818ACPZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/40页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 32-LFCSP |

| 标准包装: | 1,500 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH |

| 输入: | CML |

| 输出: | CML |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 2.7GHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

Data Sheet

ADN2817/ADN2818

Rev. E | Page 15 of 40

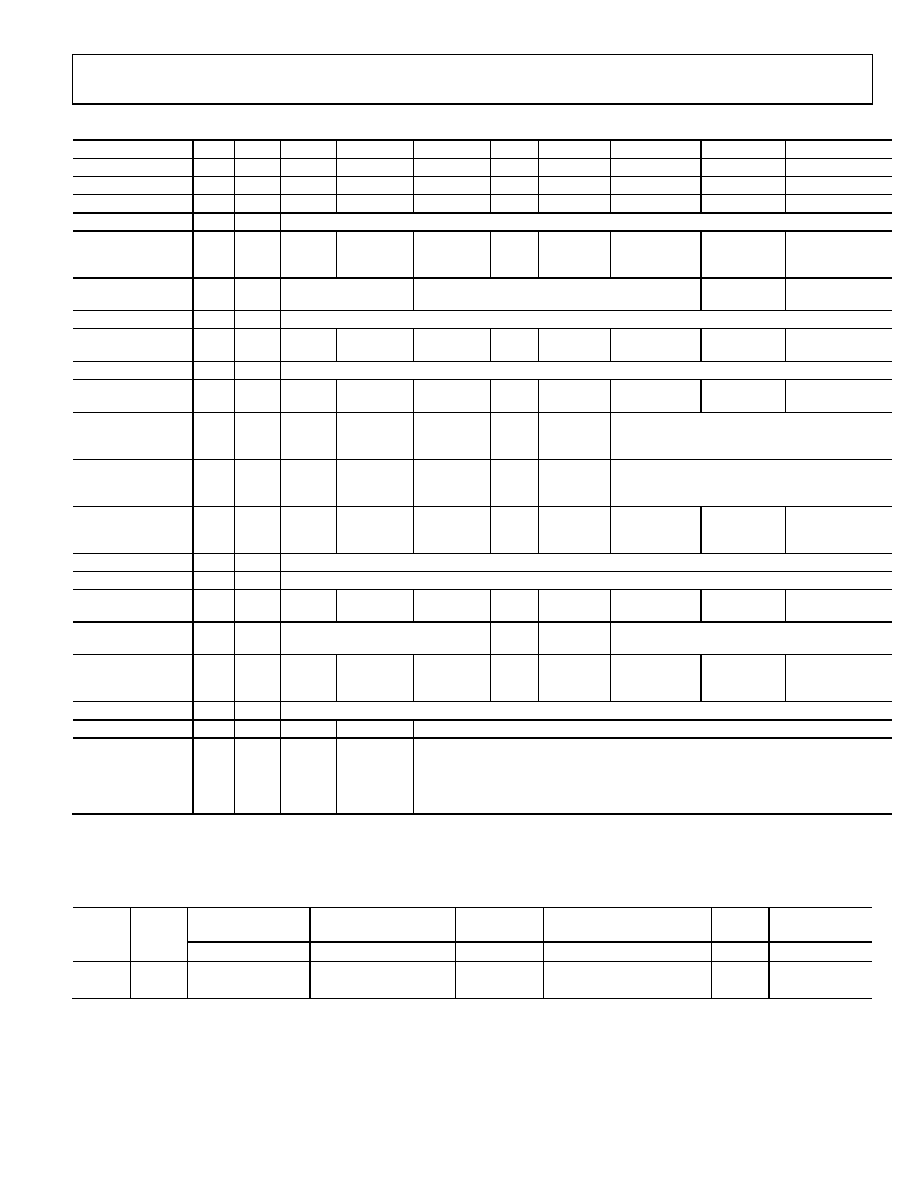

Table 8. Internal Register Map1

Reg Name

R/W

Addr

D7

D6

D5

D4

D3

D2

D1

D0

FREQ0

R

0x00

MSB

LSB

FREQ1

R

0x01

MSB

LSB

FREQ2

R

0x02

0

MSB

LSB

Rate

R

0x03

COARSE_RD[8:1]

MISC

R

0x04

X

LOS status

Static

LOL

LOL status

Data rate

measurement

complete

X

COARSE_RD[0]

(LSB)

CTRLA

W

0x08

fREF range

Data rate/DIV_FREF ratio

Measure

data rate

Lock to REFCLK

CTRLA_RD

R

0x05

Readback CTRLA

CTRLB

W

0x09

Config

LOL

Reset

MISC[4]

Initiate freq

acquisition

0

Reset

MISC[2]

0

CTRLB_RD

R

0x06

Readback CTRLB

CTRLC

W

0x11

0

Config LOS

Squelch

mode

0

CTRLD

W

0x22

CDR

bypass

Disable

DATAOUT

buffer

Disable

CLKOUT

buffer

0

Initiate

PRBS

sequence

PRBS mode

CTRLE/BERCTLB2

W

0x1F

0

Enable

BERMON

BER

stdby

mode

0

PRBS/DDR enable and output mode

SEL_MODE

W

0x34

0

Limited

rate mode

0

CLK

holdover

mode

0

HI_CODE

W

0x35

HI_CODE[8:1]

LO_CODE

W

0x36

LO_CODE[8:1]

CODE_LSB

W

0x39

0

HI_CODE[0]

(LSB)

LO_CODE[0]

(LSB)

BERCTLA

W

0x1E

BER timer (NUMBITS)

0

BER start

pulse

Error count byte select, for example, 011 = Byte 3

of 5 (NUMERRORS[39:0])

BERSTS

R

0x20

X

End of BER

measurement

(EOBM)

BER_RES

R

0x21

BER_RES[7:0], one byte of pseudo BER measurement result (NUMERRORS[39:0])

BER_DAC

R

0x24

X

BER_DAC[5:0], input to BER DAC in analog BERMON mode

Phase

W

0x37

0

Phase[5:0], twos complement sample phase adjustment,

phase code range is from 30 decimal to +30 decimal,

which gives a sampling phase offset range from 0.5 UI to +0.5 UI;

for example, phase = 111010 is6 decimal,

which gives a sampling phase offset of 6/+60 = 0.1 UI

1

X = don’t care.

2

Both CTRLE and BERCTLB registers are used, depending on the application.

Table 9. Miscellaneous Register, MISC

LOS Status

Static LOL

LOL Status

Data Rate Measurement

Complete

COARSE_RD[0]

(LSB)

D7

D6

D5

D4

D3

D2

D1

D0

X

0 = no loss of signal

0 = waiting for next LOL

0 = locked

0 = measuring data rate

X

COARSE_RD[0]

1 = loss of signal

1 = static LOL until reset

1 = acquiring

1 = measurement complete

相关PDF资料 |

PDF描述 |

|---|---|

| MS27472E24B35SA | CONN RCPT 128POS WALL MNT W/SCKT |

| MS27468T25B19P | CONN RCPT 19POS JAM NUT W/PINS |

| SY87701LZG | IC CLOCK/DATA RECOVERY 28-SOIC |

| VI-21Z-MV-F2 | CONVERTER MOD DC/DC 2V 60W |

| SY87721LHY TR | IC CLOCK/DATA RECOVERY 64-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADN2819 | 制造商:AD 制造商全称:Analog Devices 功能描述:Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2819ACP-CML | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP Tray 制造商:Rochester Electronics LLC 功能描述:MULTI-RATE 2.7GBPS CDR/ PA LOW POWER I.C - Bulk |

| ADN2819ACP-CML-RL | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP T/R |

| ADN2819ACPZ-CML | 功能描述:IC CLOCK/DATA RECOVERY 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2819ACPZ-CML1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

发布紧急采购,3分钟左右您将得到回复。