- 您现在的位置:买卖IC网 > PDF目录298814 > ADS1298RIZXGT (TEXAS INSTRUMENTS INC) SPECIALTY ANALOG CIRCUIT, PBGA64 PDF资料下载

参数资料

| 型号: | ADS1298RIZXGT |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 模拟信号调理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PBGA64 |

| 封装: | 8 X 8 MM, LEAD FREE, PLASTIC, NFBGA-64 |

| 文件页数: | 28/87页 |

| 文件大小: | 1430K |

| 代理商: | ADS1298RIZXGT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

STAR

co

TOp

de

STARTPin

DN

I

4/f

CLK

DRDY

or

t

DR

t

SETTLE

SBAS459H

– JANUARY 2010 – REVISED MAY 2011

Reset (RESET)

There are two methods to reset the ADS129x: pull the RESET pin low, or send the RESET opcode command.

When using the RESET pin, take it low to force a reset. Make sure to follow the minimum pulse width timing

specifications before taking the RESET pin back high. The RESET command takes effect on the eighth SCLK

falling edge of the opcode command. On reset it takes 18 tCLK cycles to complete initialization of the configuration

registers to the default states and start the conversion cycle. Note that an internal RESET is automatically issued

to the digital filter whenever registers CONFIG1 and RESP are set to new values with a WREG command.

START

The START pin must be set high or the START command sent to begin conversions. When START is low or if

the START command has not been sent, the device does not issue a DRDY signal (conversions are halted).

When using the START opcode to control conversion, hold the START pin low. The ADS129x feature two modes

to control conversion: continuous mode and single-shot mode. The mode is selected by SINGLE_SHOT (bit 3 of

the CONFIG4 register). In multiple device configurations the START pin is used to synchronize devices (see the

Multiple Device Configuration subsection of the SPI Interface section for more details).

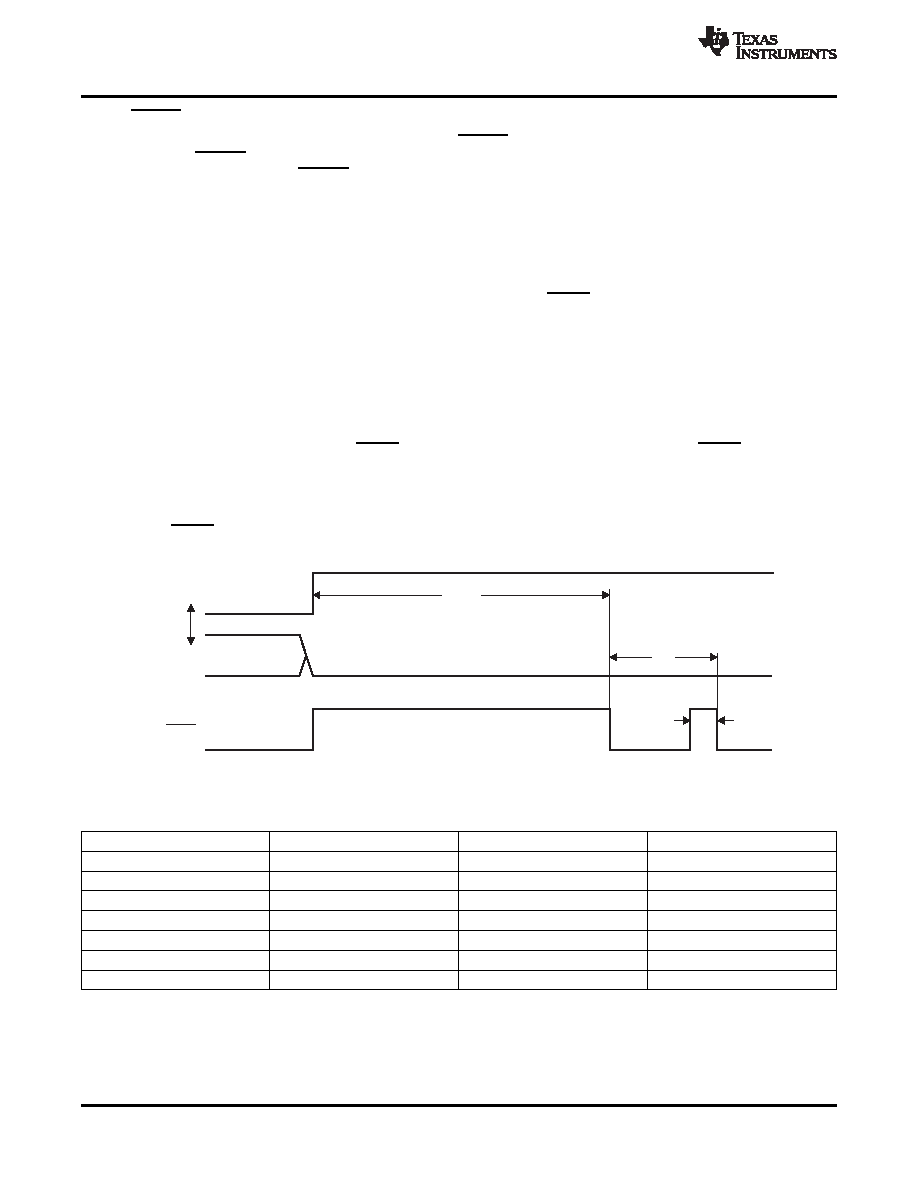

Settling Time

The settling time (tSETTLE) is the time it takes for the converter to output fully settled data when START signal is

pulled high. Once START is pulled high, DRDY is also pulled high. The next falling edge of DRDY indicates that

data are ready. Figure 40 shows the timing diagram and Table 9 shows the settling time for different data rates.

The settling time depends on fCLK and the decimation ratio (controlled by the DR[2:0] bits in the CONFIG1

register). Table 8 shows the settling time as a function of tCLK. Note that when START is held high and there is a

step change in the input signal, it takes 3

× tDR for the filter to settle to the new value. Settled data are available

on the fourth DRDY pulse. This time must be considered when trying to measure narrow PACE pulses for PACE

detection.

Figure 40. Settling Time

Table 9. Settling Times for Different Data Rates

DR[2:0]

HIGH-RESOLUTION MODE

LOW-POWER MODE

UNIT

000

296

584

tCLK

001

584

1160

tCLK

010

1160

2312

tCLK

011

2312

4616

tCLK

100

4616

9224

tCLK

101

9224

18440

tCLK

110

18440

36872

tCLK

34

Copyright

2010–2011, Texas Instruments Incorporated

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-1401TN/883B | 16-BIT, MICROPROGRAM SEQUENCER, PDIP48 |

| ADSP-21160NCB-100 | 64-BIT, 50 MHz, OTHER DSP, PBGA400 |

| ADSP-21365YSWZ-2BA | 16-BIT, 55.55 MHz, OTHER DSP, PQFP144 |

| ADSP-2181BS-160 | 24-BIT, 20 MHz, OTHER DSP, PQFP128 |

| ADUC845BCPZ8-3 | 8-BIT, FLASH, 12.58 MHz, MICROCONTROLLER, QCC56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADS1299 | 制造商:TI 制造商全称:Texas Instruments 功能描述:Low-Noise, 8-Channel, 24-Bit Analog Front-End for Biopotential Measurements |

| ADS1299_1211 | 制造商:TI 制造商全称:Texas Instruments 功能描述:Low-Noise, 8-Channel, 24-Bit Analog Front-End for Biopotential Measurements |

| ADS1299-4PAG | 功能描述:IC AFE 4-CH 24BIT 64TQFP 制造商:texas instruments 系列:- 包装:托盘 零件状态:在售 位数:24 通道数:4 电压 - 电源,模拟:5V 电压 - 电源,数字:1.8 V ~ 3.6 V 封装/外壳:64-TQFP 供应商器件封装:64-TQFP(10x10) 标准包装:160 |

| ADS1299-4PAGR | 功能描述:IC AFE 4-CH 24BIT 64TQFP 制造商:texas instruments 系列:- 包装:剪切带(CT) 零件状态:在售 位数:24 通道数:4 功率(W):24mW 电压 - 电源,模拟:4.75 V ~ 5.25 V 电压 - 电源,数字:1.8 V ~ 3.6 V 封装/外壳:64-TQFP 供应商器件封装:64-TQFP(10x10) 标准包装:1 |

| ADS1299-6PAG | 功能描述:IC AFE 6-CH 24BIT 64TQFP 制造商:texas instruments 系列:- 包装:托盘 零件状态:在售 位数:24 通道数:6 功率(W):33mW 电压 - 电源,模拟:5V 电压 - 电源,数字:1.8 V ~ 3.6 V 封装/外壳:64-TQFP 供应商器件封装:64-TQFP(10x10) 标准包装:160 |

发布紧急采购,3分钟左右您将得到回复。