- 您现在的位置:买卖IC网 > PDF目录19376 > ADSP-21061KSZ-133 (Analog Devices Inc)IC DSP CONTROLLER 32BIT 240MQFP PDF资料下载

参数资料

| 型号: | ADSP-21061KSZ-133 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 23/52页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 32BIT 240MQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | 同步串行端口(SSP) |

| 时钟速率: | 33MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 128kB |

| 电压 - 输入/输出: | 5.00V |

| 电压 - 核心: | 5.00V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 240-BFQFP 裸露焊盘 |

| 供应商设备封装: | 240-MQFP-EP(32x32) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

Rev. D | Page 3 of 52 | May 2013

GENERAL DESCRIPTION

The ADSP-21061 SHARC—Super Harvard Architecture Com-

puter—is a signal processing microcomputer that offers new

capabilities and levels of performance. The ADSP-21061

SHARC is a 32-bit processor optimized for high performance

DSP applications. The ADSP-21061 builds on the ADSP-21000

DSP core to form a complete system-on-a-chip, adding a dual-

ported on-chip SRAM and integrated I/O peripherals supported

by a dedicated I/O bus.

Fabricated in a high speed, low power CMOS process, the

ADSP-21061 has a 20 ns instruction cycle time and operates at

50 MIPS. With its on-chip instruction cache, the processor can

execute every instruction in a single cycle. Table 1 shows perfor-

mance benchmarks for the ADSP-21061/ADSP-21061L.

The ADSP-21061 SHARC represents a new standard of integra-

tion for signal computers, combining a high performance

floating-point DSP core with integrated, on-chip system fea-

tures including 1M bit SRAM memory, a host processor

interface, a DMA controller, serial ports, and parallel bus con-

nectivity for glueless DSP multiprocessing.

The ADSP-21061 continues SHARC’s industry-leading stan-

dards of integration for DSPs, combining a high performance

32-bit DSP core with integrated, on-chip system features.

The block diagram on Page 1, illustrates the following architec-

tural features:

Computation units (ALU, multiplier, and shifter) with a

shared data register file

Data address generators (DAG1, DAG2)

Program sequencer with instruction cache

PM and DM buses capable of supporting four 32-bit data

transfers between memory and the core at every core pro-

cessor cycle

Interval timer

On-chip SRAM

External port for interfacing to off-chip memory and

peripherals

Host port and multiprocessor interface

DMA controller

Serial ports

JTAG test access port

SHARC FAMILY CORE ARCHITECTURE

The ADSP-21061 includes the following architectural features

of the ADSP-21000 family core. The ADSP-21061 processors

are code- and function-compatible with the ADSP-21020,

ADSP-21060, and ADSP-21062 SHARC processors.

Independent, Parallel Computation Units

The arithmetic/logic unit (ALU), multiplier, and shifter all per-

form single-cycle instructions. The three units are arranged in

parallel, maximizing computational throughput. Single multi-

function instructions execute parallel ALU and multiplier oper-

ations. These computation units support IEEE 32-bit single-

precision floating-point, extended-precision 40-bit floating-

point, and 32-bit fixed-point data formats.

Data Register File

A general-purpose data register file is used for transferring data

between the computation units and the data buses, and for stor-

ing intermediate results. This 10-port, 32-register (16 primary,

16 secondary) register file, combined with the ADSP-21000

Harvard architecture, allows unconstrained data flow between

computation units and internal memory.

Table 1. Benchmarks (at 50 MHz)

Benchmark Algorithm

Speed

Cycles

1024 Point Complex FFT (Radix 4,

with reversal)

.37 ms

18,221

FIR Filter (per tap)

20 ns

1

IIR Filter (per biquad)

80 ns

4

Divide (y/x)

120 ns

6

Inverse Square Root

180 ns

9

DMA Transfer Rate

300M bps

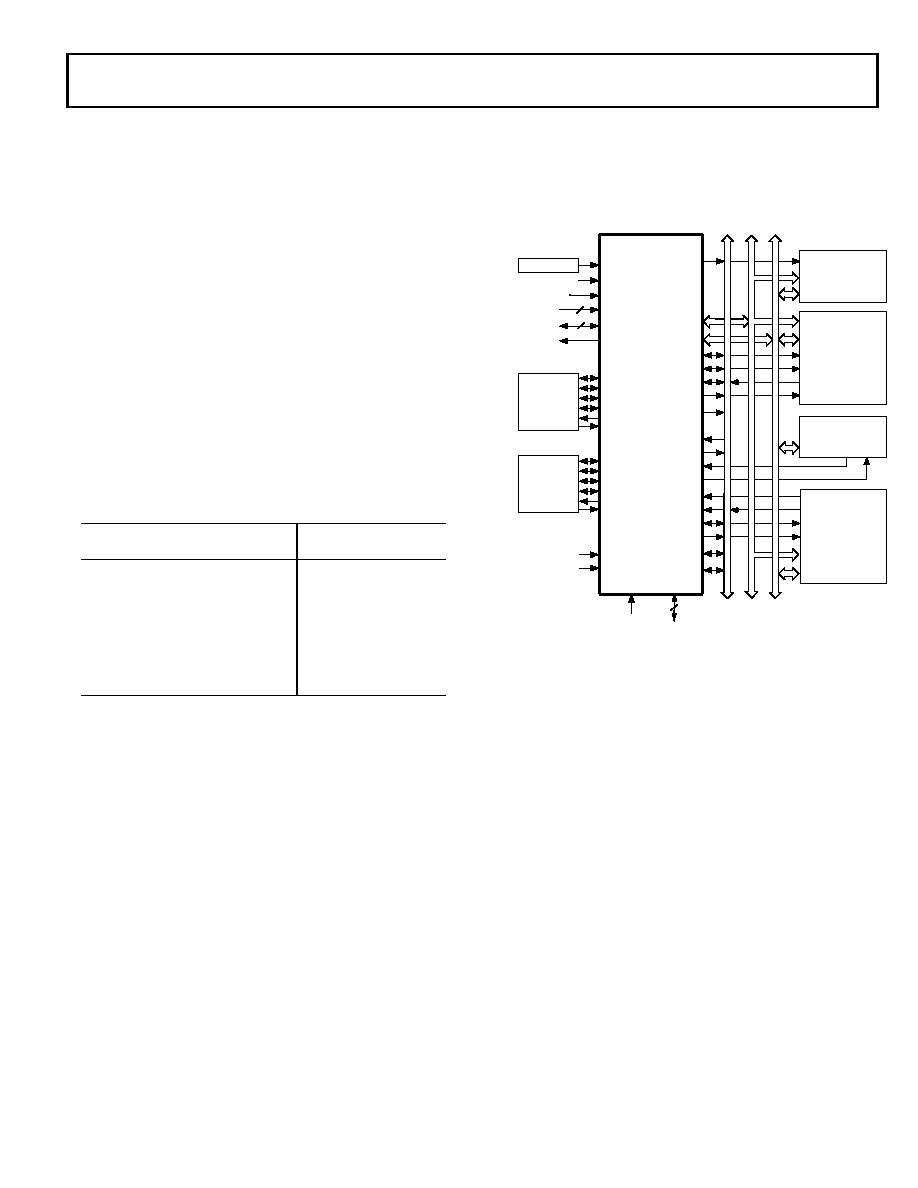

Figure 2. ADSP-21061/ADSP-21061L System Sample Configuration

3

4

RESET

JTAG

7

ADSP-21061

BMS

1

CLOCK

CS

BOOT

EPROM

(OPTIONAL)

MEMORY-

MAPPED

DEVICES

(OPTIONAL)

OE

DATA

DMA DEVICE

(OPTIONAL)

DATA

ADDR

DATA

HOST

PROCESSOR

INTERFACE

(OPTIONAL)

CS

RD

PAGE

ADRCLK

ACK

BR

1–6

DMAR

1–2

CLKIN

IRQ

2–0

TCLK0

RPBA

EBOOT

LBOOT

FLAG

3–0

TIMEXP

DR0

DT0

RSF0

TFS0

RCLK0

TCLK1

DR1

DT1

RSF1

TFS1

RCLK1

ID

2–0

SERIAL

DEVICE

(OPTIONAL)

SERIAL

DEVICE

(OPTIONAL)

CPA

REDY

HBG

HBR

DMAG

1–2

SBTS

MS3–0

WR

DATA

47–0

DATA

ADDR

CS

ACK

WE

ADDR

31–0

D

A

T

A

C

O

N

T

R

O

L

A

D

R

E

S

ADDR

TO GND

SW

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B31-CY-F2 | CONVERTER MOD DC/DC 12V 50W |

| TAJY156M025RNJ | CAP TANT 15UF 25V 20% 2917 |

| 5717-RC | CHOKE RF HI CURR 500UH 15% RAD |

| VI-B30-CY-F2 | CONVERTER MOD DC/DC 5V 50W |

| MAX6665ASA70+T | IC FAN CNTRL/DRVR 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21061KSZ-160 | 功能描述:IC DSP CONTROLLER 1MBIT 240MQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21061KSZ-200 | 功能描述:IC DSP CONTROLLER 32BIT 240MQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21061L | 制造商:Analog Devices 功能描述: |

| ADSP-21061LAS-160 | 制造商:AD 制造商全称:Analog Devices 功能描述:ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21061LAS-176 | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 44MHz 44MIPS 240-Pin MQFP Tray 制造商:Analog Devices 功能描述:IC MICROCOMPUTER DSP |

发布紧急采购,3分钟左右您将得到回复。