- 您现在的位置:买卖IC网 > PDF目录19376 > ADSP-21061KSZ-133 (Analog Devices Inc)IC DSP CONTROLLER 32BIT 240MQFP PDF资料下载

参数资料

| 型号: | ADSP-21061KSZ-133 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/52页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 32BIT 240MQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | 同步串行端口(SSP) |

| 时钟速率: | 33MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 128kB |

| 电压 - 输入/输出: | 5.00V |

| 电压 - 核心: | 5.00V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 240-BFQFP 裸露焊盘 |

| 供应商设备封装: | 240-MQFP-EP(32x32) |

| 包装: | 托盘 |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

Rev. D | Page 11 of 52 | May 2013

TFSx

I/O

Transmit Frame Sync (Serial Ports 0, 1).

RFSx

I/O

Receive Frame Sync (Serial Ports 0, 1).

EBOOT

I

EPROM Boot Select.

When EBOOT is high, the ADSP-21061 is configured for booting from an 8-bit EPROM.

When EBOOT is low, the LBOOT and BMS inputs determine booting mode. See the table in the BMS pin

description below. This signal is a system configuration selection that should be hardwired.

LBOOT

I

Link Boot.

Must be tied to GND.

BMS

I/O/T*

Boot Memory Select. Output

: Used as chip select for boot EPROM devices (when EBOOT = 1,

LBOOT = 0). In a multiprocessor system, BMS is output by the bus master. Input: When low, indicates that no

booting will occur and that ADSP-21061 will begin executing instructions from external memory. See table

below. This input is a system configuration selection that should be hardwired. *Three-statable only in

EPROM boot mode (when BMS is an output).

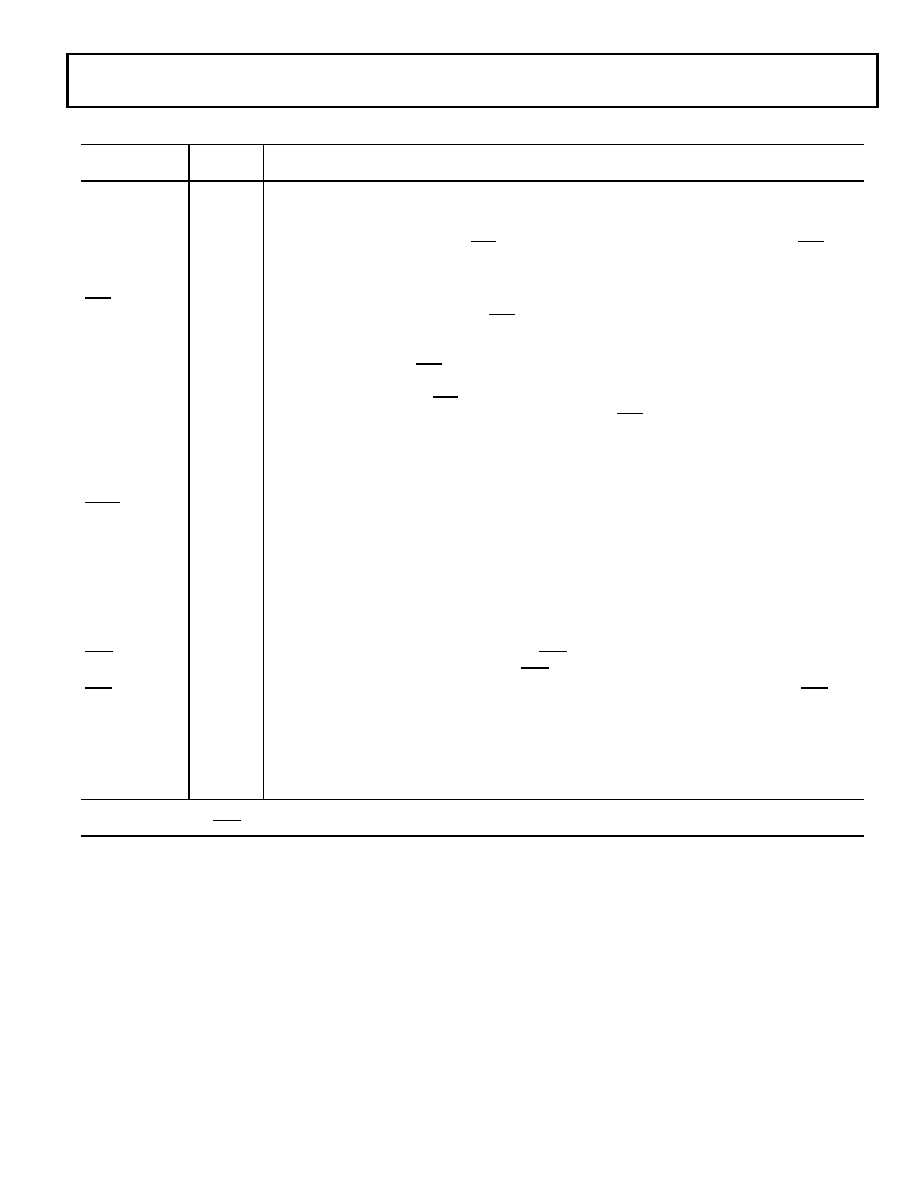

EBOOT

LBOOT

BMS

Booting Mode

1

0

Output

EPROM (Connect BMS to EPROM chip select.)

0

1(Input)

Host Processor.

0

0 (Input)

No Booting. Processor executes from external memory.

CLKIN

I

Clock In.

External clock input to the ADSP-21061. The instruction cycle rate is equal to CLKIN. CLKIN may

not be halted, changed, or operated below the minimum specified frequency.

RESET

I/A

Processor Reset.

Resets the ADSP-21061 to a known state and begins program execution at the program

memory location specified by the hardware reset vector address. This input must be asserted (low) at

power-up.

TCK

I

Test Clock (JTAG).

Provides an asynchronous clock for JTAG boundary scan.

TMS

I/S

Test Mode Select (JTAG).

Used to control the test state machine. TMS has a 20 k internal pull-up resistor.

TDI

I/S

Test Data Input (JTAG).

Provides serial data for the boundary scan logic. TDI has a 20 k internal pull-up

resistor.

TDO

O

Test Data Output (JTAG).

Serial scan output of the boundary scan path.

TRST

I/A

Test Reset (JTAG).

Resets the test state machine. TRST must be asserted (pulsed low) after power-up or held

low for proper operation of the ADSP-21061. TRST has a 20 k internal pull-up resistor.

EMU

O

Emulation Status.

Must be connected to the ADSP-21061 EZ-ICE target board connector only. EMU has a

50 k internal pull-up resistor.

ICSA

O

Reserved.

Leave unconnected.

VDD

P

Power Supply

. (30 pins). See Operating Conditions (5 V) and Operating Conditions (3.3 V).

GND

G

Power Supply Return.

(30 pins)

NC

Do Not Connect.

Reserved pins which must be left open and unconnected.

Table 2. Pin Descriptions (Continued)

Pin

Type

Function

A = Asynchronous, G = Ground, I = Input, O = Output, P = Power Supply, S = Synchronous, (A/D) = Active Drive, (O/D) = Open-Drain,

T = Three-State (when SBTS is asserted, or when the ADSP-21061 is a bus slave)

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B31-CY-F2 | CONVERTER MOD DC/DC 12V 50W |

| TAJY156M025RNJ | CAP TANT 15UF 25V 20% 2917 |

| 5717-RC | CHOKE RF HI CURR 500UH 15% RAD |

| VI-B30-CY-F2 | CONVERTER MOD DC/DC 5V 50W |

| MAX6665ASA70+T | IC FAN CNTRL/DRVR 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21061KSZ-160 | 功能描述:IC DSP CONTROLLER 1MBIT 240MQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21061KSZ-200 | 功能描述:IC DSP CONTROLLER 32BIT 240MQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21061L | 制造商:Analog Devices 功能描述: |

| ADSP-21061LAS-160 | 制造商:AD 制造商全称:Analog Devices 功能描述:ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21061LAS-176 | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 44MHz 44MIPS 240-Pin MQFP Tray 制造商:Analog Devices 功能描述:IC MICROCOMPUTER DSP |

发布紧急采购,3分钟左右您将得到回复。