- 您现在的位置:买卖IC网 > PDF目录19466 > ADSP-21065LKSZ-240 (Analog Devices Inc)IC DSP CONTROLLR 544KBIT 208MQFP PDF资料下载

参数资料

| 型号: | ADSP-21065LKSZ-240 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 17/44页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLR 544KBIT 208MQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | 主机接口,串行端口 |

| 时钟速率: | 60MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 64kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 3.30V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-MQFP(28x28) |

| 包装: | 托盘 |

| 其它名称: | ADSP-21065LKSZ240 ADSP-21065LKSZ240-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

REV. C

ADSP-21065L

–24–

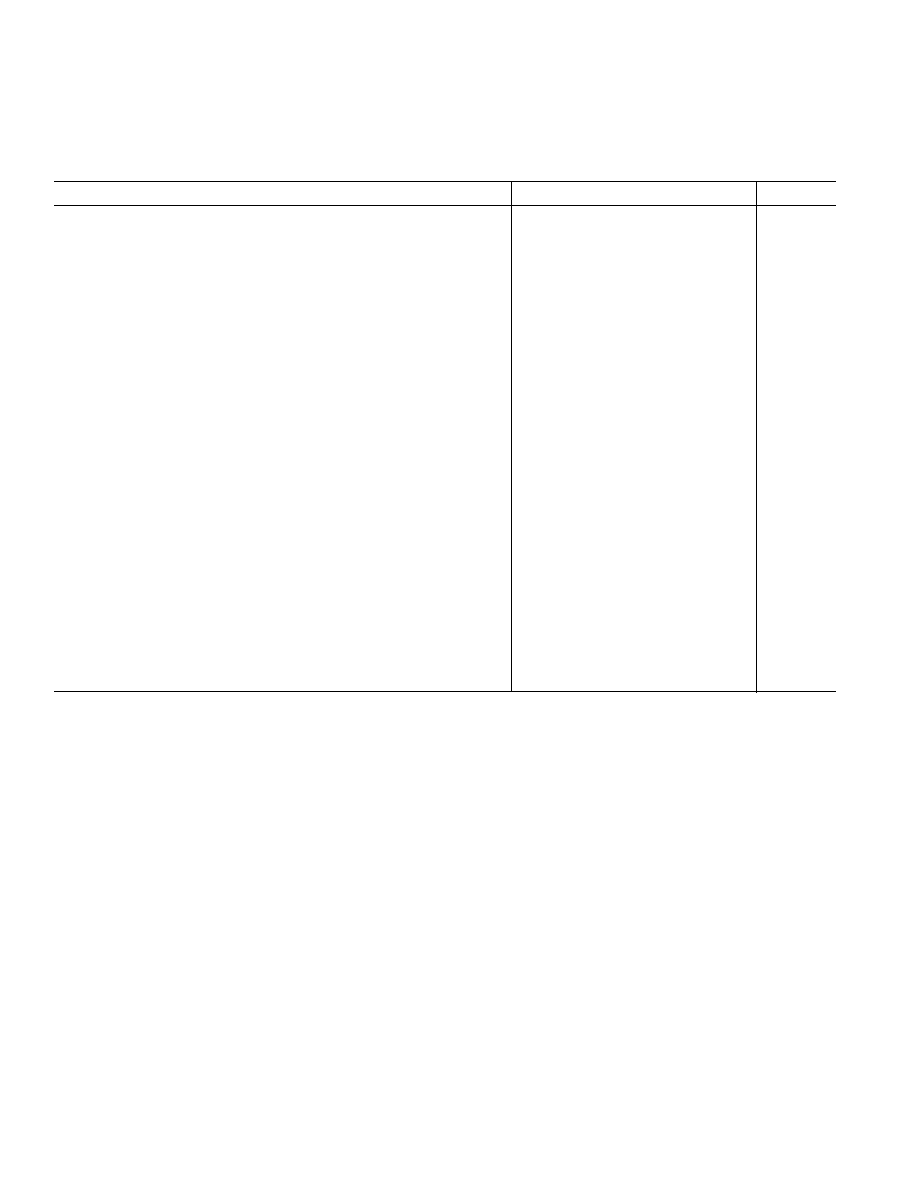

Asynchronous Read/Write—Host to ADSP-21065L

Use these specifications for asynchronous host processor accesses of an ADSP-21065L, after the host has asserted

CS and HBR

(low). After the ADSP-21065L returns

HBG, the host can drive the RD and WR pins to access the ADSP-21065L’s IOP registers.

HBR and HBG are assumed low for this timing. Writes can occur at a minimum interval of (1/2) t

CK.

Parameter

Min

Max

Unit

Read Cycle

Timing Requirements:

tSADRDL

Address Setup/CS Low Before RD Low*

0.0

ns

tHADRDH

Address Hold/

CS Hold Low After RD High

0.0

ns

tWRWH

RD/WR High Width

6.0

ns

tDRDHRDY

RD High Delay After REDY (O/D) Disable

0.0

ns

tDRDHRDY

RD High Delay After REDY (A/D) Disable

0.0

ns

Switching Characteristics:

tSDATRDY

Data Valid Before REDY Disable from Low

1.5

ns

tDRDYRDL

REDY (O/D) or (A/D) Low Delay After

RD Low

13.5

ns

tRDYPRD

REDY (O/D) or (A/D) Low Pulsewidth for Read

28.0 + DT

ns

tHDARWH

Data Disable After

RD High

2.0

10.0

ns

Write Cycle

Timing Requirements:

tSCSWRL

CS Low Setup Before WR Low

0.0

ns

tHCSWRH

CS Low Hold After WR High

0.0

ns

tSADWRH

Address Setup Before

WR High

5.0

ns

tHADWRH

Address Hold After

WR High

2.0

ns

tWWRL

WR Low Width

7.0

ns

tWRWH

RD/WR High Width

6.0

ns

tDWRHRDY

WR High Delay After REDY (O/D) or (A/D) Disable

0.0

ns

tSDATWH

Data Setup Before

WR High

5.0

ns

tHDATWH

Data Hold After

WR High

1.0

ns

Switching Characteristics:

tDRDYWRL

REDY (O/D) or (A/D) Low Delay After

WR/CS Low

13.5

ns

tRDYPWR

REDY (O/D) or (A/D) Low Pulsewidth for Write

7.75

ns

NOTE

*Not required if RD and address are valid tHBGRCSV after HBG goes low. For first access after HBR asserted, ADDR23-0 must be a nonMMS value 1/2 tCLK before

RD or WR goes low or by t

HBGRCSV after HBG goes low. This is easily accomplished by driving an upper address signal high when HBG is asserted. See Host Inter-

face, in the ADSP-21065L SHARC User’s Manual, Second Edition.

相关PDF资料 |

PDF描述 |

|---|---|

| GEC07DRTI | CONN EDGECARD 14POS DIP .100 SLD |

| TAP106M035DCS | CAP TANT 10UF 35V 20% RADIAL |

| HMM36DRTF | CONN EDGECARD 72POS DIP .156 SLD |

| VI-B12-CW-B1 | CONVERTER MOD DC/DC 15V 100W |

| VE-21K-CY-F3 | CONVERTER MOD DC/DC 40V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21065LKSZ-264 | 功能描述:IC DSP CONTROLL 544KBIT 208-MQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-2106X | 制造商:AD 制造商全称:Analog Devices 功能描述:DSP Microcomputer Family |

| ADSP-2109 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost DSP Microcomputers |

| ADSP-2109KP-80 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost DSP Microcomputers |

| ADSP-2109LKP-55 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost DSP Microcomputers |

发布紧急采购,3分钟左右您将得到回复。