- 您现在的位置:买卖IC网 > PDF目录19466 > ADSP-21065LKSZ-240 (Analog Devices Inc)IC DSP CONTROLLR 544KBIT 208MQFP PDF资料下载

参数资料

| 型号: | ADSP-21065LKSZ-240 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 26/44页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLR 544KBIT 208MQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | 主机接口,串行端口 |

| 时钟速率: | 60MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 64kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 3.30V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-MQFP(28x28) |

| 包装: | 托盘 |

| 其它名称: | ADSP-21065LKSZ240 ADSP-21065LKSZ240-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

REV. C

ADSP-21065L

–32–

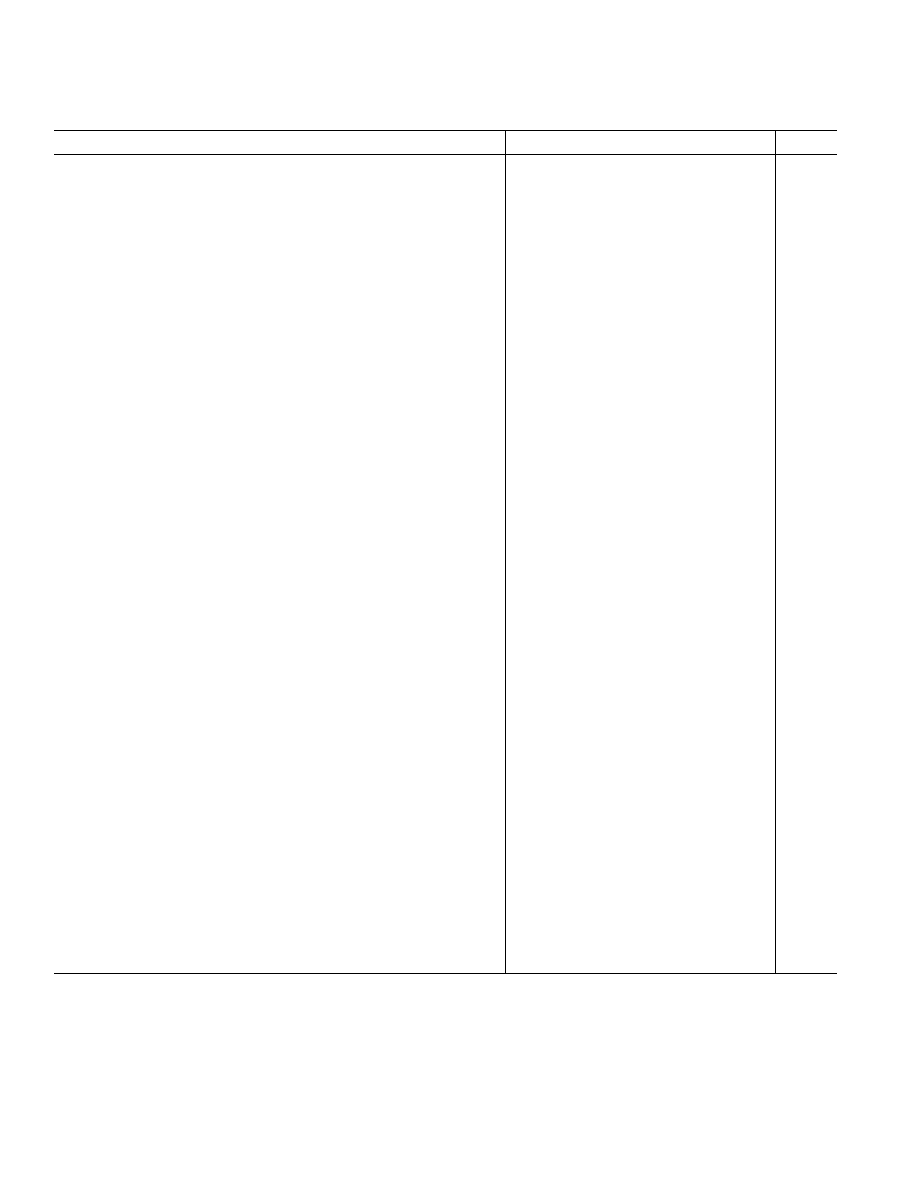

Serial Ports

Parameter

Min

Max

Unit

External Clock

Timing Requirements:

tSFSE

TFS/RFS Setup Before TCLK/RCLK

1

4.0

ns

tHFSE

TFS/RFS Hold After TCLK/RCLK

1

4.0

ns

tSDRE

Receive Data Setup Before RCLK

1

1.5

ns

tHDRE

Receive Data Hold After RCLK

1

4.0

ns

tSCLKW

TCLK/RCLK Width

9.0

ns

tSCLK

TCLK/RCLK Period

tCK

ns

Internal Clock

Timing Requirements:

tSFSI

TFS Setup Before TCLK

2; RFS Setup Before RCLK1

8.0

ns

tHFSI

TFS/RFS Hold After TCLK/RCLK

1

1.0

ns

tSDRI

Receive Data Setup Before RCLK

1

3.0

ns

tHDRI

Receive Data Hold After RCLK

1

3.0

ns

External or Internal Clock

Switching Characteristics:

tDFSE

RFS Delay After RCLK (Internally Generated RFS)

2

13.0

ns

tHOFSE

RFS Hold After RCLK (Internally Generated RFS)

2

3.0

ns

External Clock

Switching Characteristics:

tDFSE

TFS Delay After TCLK (Internally Generated TFS)

2

13.0

ns

tHOFSE

TFS Hold After TCLK (Internally Generated TFS)

2

3.0

ns

tDDTE

Transmit Data Delay After TCLK

2

12.5

ns

tHDTE

Transmit Data Hold After TCLK

2

4.0

ns

Internal Clock

Switching Characteristics:

tDFSI

TFS Delay After TCLK (Internally Generated TFS)

2

4.5

ns

tHOFSI

TFS Hold After TCLK (Internally Generated TFS)

2

–1.5

ns

tDDTI

Transmit Data Delay After TCLK

2

7.5

ns

tHDTI

Transmit Data Hold After TCLK

2

0.0

ns

tSCLKIW

TCLK/RCLK Width

(tSCLK/2) – 2.5

(tSCLK/2) + 2.5

ns

Enable and Three-State

Switching Characteristics:

tDTENE

Data Enable from External TCLK

2

5.0

ns

tDDTTE

Data Disable from External RCLK

2

10.0

ns

tDTENI

Data Enable from Internal TCLK

2

0.0

ns

tDDTTI

Data Disable from Internal TCLK

2

3.0

ns

tDCLK

TCLK/RCLK Delay from CLKIN

18.0 + 6 DT

ns

tDPTR

SPORT Disable After CLKIN

14.0

ns

External Late Frame Sync

tDDTLFSE

Data Delay from Late External TFS or External RFS

with MCE = 1, MFD = 0

3, 4

10.5

ns

tDTENLFSE

Data Enable from late FS or MCE = 1, MFD = 0

3, 4

3.5

ns

tDDTLSCK

Data Delay from TCLK/RCLK for Late External

TFS or External RFS with MCE = 1, MFD = 0

3, 4

12.0

ns

tDTENLSCK

Data Enable from RCLK/TCLK for Late External FS or

MCE = 1, MFD = 0

3, 4

4.5

ns

NOTES

To determine whether communication is possible between two devices at clock speed n, the following specifications must be confirmed: 1) frame sync delay and frame

sync setup-and-hold, 2) data delay and data setup-and-hold, and 3) SCLK width.

1Referenced to sample edge.

2Referenced to drive edge.

3MCE = 1, TFS enable and TFS valid follow t

DDTENFS and tDDTLFSE.

4If external RFS/TFS setup to RCLK/TCLK > t

SCLK/2 then tDDTLSCK and tDTENLSCK apply; otherwise tDDTLFSE and tDTENLFS apply.

*Word selected timing for I

2S mode is the same as TFS/RFS timing (normal framing only).

相关PDF资料 |

PDF描述 |

|---|---|

| GEC07DRTI | CONN EDGECARD 14POS DIP .100 SLD |

| TAP106M035DCS | CAP TANT 10UF 35V 20% RADIAL |

| HMM36DRTF | CONN EDGECARD 72POS DIP .156 SLD |

| VI-B12-CW-B1 | CONVERTER MOD DC/DC 15V 100W |

| VE-21K-CY-F3 | CONVERTER MOD DC/DC 40V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21065LKSZ-264 | 功能描述:IC DSP CONTROLL 544KBIT 208-MQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-2106X | 制造商:AD 制造商全称:Analog Devices 功能描述:DSP Microcomputer Family |

| ADSP-2109 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost DSP Microcomputers |

| ADSP-2109KP-80 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost DSP Microcomputers |

| ADSP-2109LKP-55 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Cost DSP Microcomputers |

发布紧急采购,3分钟左右您将得到回复。