- 您现在的位置:买卖IC网 > PDF目录223311 > ADSP-2191MKSTZ-160 (ANALOG DEVICES INC) 16-bit Fixed-Point DSP, 160 MIPS, 160K bytes RAM; Package: 144 ld LQFP (20x20mm); No of Pins: 144; Temperature Range: Comm. PDF资料下载

参数资料

| 型号: | ADSP-2191MKSTZ-160 |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 16-bit Fixed-Point DSP, 160 MIPS, 160K bytes RAM; Package: 144 ld LQFP (20x20mm); No of Pins: 144; Temperature Range: Comm. |

| 中文描述: | 16-BIT, 100 MHz, OTHER DSP, PQFP144 |

| 封装: | PLASTIC, LQFP-144 |

| 文件页数: | 15/48页 |

| 文件大小: | 1789K |

| 代理商: | ADSP-2191MKSTZ-160 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

ADSP-2191M

–22–

REV. A

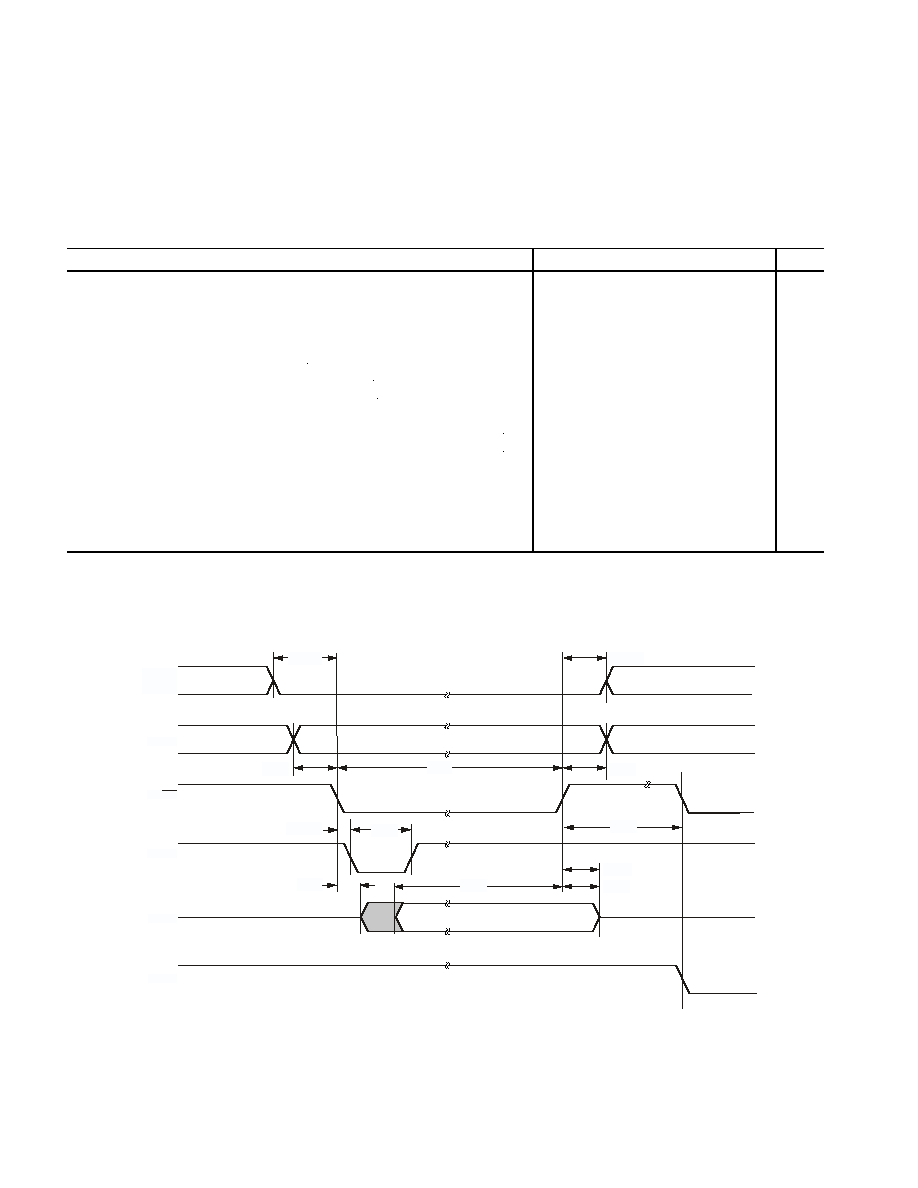

External Port Write Cycle Timing

The external port lets systems extend read/write accesses in three

ways: waitstates, ACK input, and combined waitstates and ACK.

To add waits with ACK, the DSP must see ACK low at the rising

edge of EMI clock. ACK low causes the DSP to wait, and the

DSP requires two EMI clock cycles after ACK goes high to finish

the access. For more information, see the External Port chapter

in the ADSP-219x/ADSP-2191 DSP Hardware Reference.

Table 12. External Port Write Cycle Timing

Parameter1, 2

Min

Max

Unit

Switching Characteristics

t

CSWS

Chip Select Asserted to

WR Asserted Delay

0.5t

HCLK –4

ns

t

AWS

Address Valid to

WR Setup and Delay

0.5t

HCLK –3

ns

t

WSCS

WR Deasserted to Chip Select Deasserted

0.5t

HCLK –4

ns

t

WSA

WR Deasserted to Address Invalid

0.5t

HCLK –3

ns

t

WW

WR Strobe Pulsewidth

t

HCLK –2+ W

3

ns

t

CDA

WR to Data Enable Access Delay

0ns

t

CDD

WR to Data Disable Access Delay

0.5t

HCLK – 3

0.5t

HCLK +4

ns

t

DSW

Data Valid to

WR Deasserted Setup

t

HCLK +1+W

3

t

HCLK +7+W

3

ns

t

DHW

WR Deasserted to Data Invalid Hold Time; E_WHC4

3.4

ns

t

DHW

WR Deasserted to Data Invalid Hold Time; E_WHC4

t

HCLK +3.4

ns

t

WWR

WR Deasserted to WR, RD Asserted

t

HCLK

Timing Requirements

t

AKW

ACK Strobe Pulsewidth

12.5

ns

t

DWSAK

ACK Delay from

WR Low

0

ns

1t

HCLK is the peripheral clock period.

2These are timing parameters that are based on worst-case operating conditions.

3W = (number of waitstates specified in wait register)

tHCLK.

4Write hold cycle–memory select control registers (MS

CTL).

Figure 11. External Port Write Cycle Timing

D 15–0

tAW S

tWW

tAKW

tDH W

tCD D

AC K

WR

A 21–0

M S 3–0

IO M S

BM S

tCSW S

tWS A

tWS C S

tCD A

tDW SA K

RD

tDS W

tWW R

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-21990BSTZ | High-Performance Mixed-Signal DSP, 160 MHz, 4K Words Program Memory RAM; Package: LQFP 1.4 MM; No of Pins: 176; Temperature Range: Ind |

| ADSP-BF542BBCZ-4A | 400 MHz Blackfin Embedded Processor: ADSP-BF542BBCZ-4A Temp Range: –40°C to +85°C Package: 400-Ball CSP_BGA BC-400-1 |

| ADSP-BF542BBCZ-5A | 533 MHz Blackfin Embedded Processor: ADSP-BF542BBCZ-5A Temp Range: –40°C to +85°C Package: 400-Ball CSP_BGA BC-400-1 |

| ADSP-BF542MBBCZ-5M | 533 MHz Blackfin Embedded Processor: ADSP-BF542MBBCZ-5M Temp Range: –40°C to +85°C Package: 400-Ball CSP_BGA BC-400-1 |

| ADSP-BF542KBCZ-6A | 600 MHz Blackfin Embedded Processor: ADSP-BF542KBCZ-6A Temp Range: 0°C to +70°C Package: 400-Ball CSP_BGA BC-400-1 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-2195MBCA-140 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 24-Bit 140MHz 140MIPS 144-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:16-BIT,140 MIPS, 2.5V, 80KBYTES RAM - Bulk |

| ADSP-2195MBST-140 | 功能描述:IC DSP CONTROLLER 16BIT 144LQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:ADSP-21xx 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-2195MKCA-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 24-Bit 160MHz 160MIPS 144-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:16-BIT,160 MIPS, 2.5V, 80KBYTES RAM - Bulk |

| ADSP-2195MKST-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 24-Bit 160MHz 160MIPS 144-Pin LQFP 制造商:Analog Devices 功能描述:IC MICROCOMPUTER 16-BIT |

| adsp-2196mbca-140 | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。