参数资料

| 型号: | ADSP-21992YBC |

| 厂商: | Analog Devices Inc |

| 文件页数: | 6/60页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTLR 16BIT 196CSPBGA |

| 标准包装: | 1 |

| 系列: | ADSP-21xx |

| 类型: | 定点 |

| 接口: | SPI,SSP |

| 时钟速率: | 150MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 128kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 2.50V |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 196-BGA |

| 供应商设备封装: | 196-MBGA(15x15) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

Rev. A

|

Page 14 of 60

|

August 2007

ADSP-21992

from an external source using the RESET signal, or alterna-

tively, the internal power-on reset circuit may be used by

connecting the POR pin to the RESET pin. During power-up

the RESET line must be activated for long enough to allow the

DSP core’s internal clock to stabilize. The power-up sequence is

defined as the total time required for the crystal oscillator to sta-

bilize after a valid VDD is applied to the processor and for the

internal phase-locked loop (PLL) to lock onto the specific crys-

tal frequency. A minimum of 512 cycles will ensure that the PLL

has locked (this does not include the crystal oscillator

start-up time).

The RESET input contains some hysteresis. If an RC circuit is

used to generate the RESET signal, the circuit should use an

external Schmitt trigger.

The master reset sets all internal stack pointers to the empty

stack condition, masks all interrupts, and resets all registers to

their default values (where applicable). When RESET is

released, if there is no pending bus request, program control

jumps to the location of the on-chip boot ROM (0xFF0000) and

the booting sequence is performed.

POWER SUPPLIES

The ADSP-21992 has separate power supply connections for the

internal (VDDINT) and external (VDDEXT) power supplies. The

internal supply must meet the 2.5 V requirement. The external

supply must be connected to a 3.3 V supply. All external supply

pins must be connected to the same supply. The ideal power-on

sequence for the DSP is to provide power-up of all supplies

simultaneously. If there is going to be some delay in power-up

between the supplies, provide VDD first, then VDD_IO.

BOOTING MODES

The ADSP-21992 supports a number of different boot modes

that are controlled by the three dedicated hardware boot mode

control pins (BMODE2, BMODE1, and BMODE0). The use of

three boot mode control pins means that up to eight different

boot modes are possible. Of these only five modes are valid on

the ADSP-21992. The ADSP-21992 exposes the boot mecha-

nism to software control by providing a nonmaskable boot

interrupt that vectors to the start of the on-chip ROM memory

block (at address 0xFF0000). A boot interrupt is automatically

initiated following either a hardware initiated reset, via the

RESET pin, or a software initiated reset, via writing to the soft-

ware reset register. Following either a hardware or a software

reset, execution always starts from the boot ROM at address

0xFF0000, irrespective of the settings of the BMODE2,

BMODE1, and BMODE0 pins. The dedicated BMODE2,

BMODE1, and BMODE0 pins are sampled at hardware reset.

The particular boot mode for the ADSP-21992 associated with

the settings of the BMODE2, BMODE1, BMODE0 pins is

defined in Table 3.

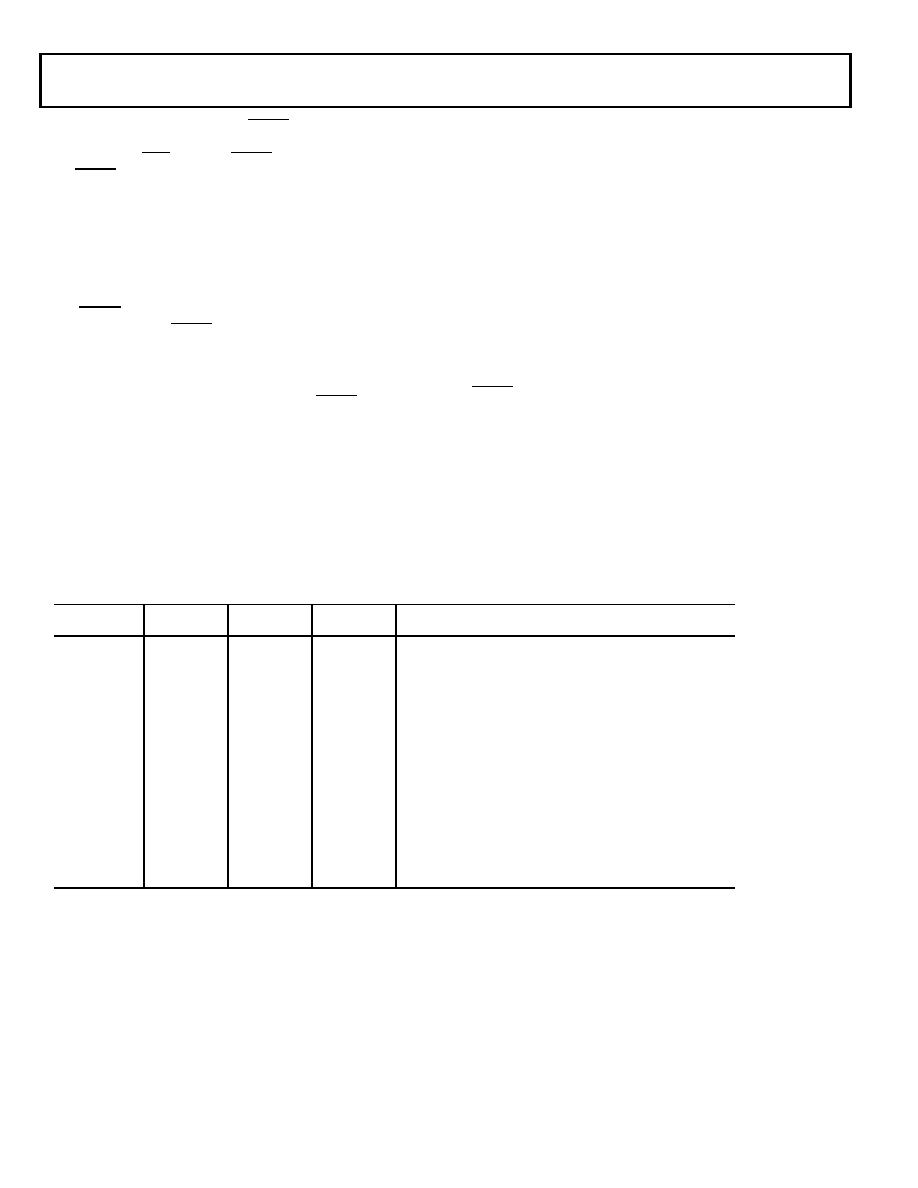

Table 3. Summary of Boot Modes

Boot Mode

BMODE2

BMODE1

BMODE0

Function

0

Illegal–Reserved

1

0

1

Boot from External 8-Bit Memory over EMI

2

0

1

0

Execute from External 8-Bit Memory

3

0

1

Execute from External 16-Bit Memory

4

1

0

Boot from SPI

≤ 4K Bits

5

1

0

1

Boot from SPI

> 4K Bits

6

1

0

Illegal–Reserved

7

1

Illegal–Reserved

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-3PARCBF548M01 | MODULE BOARD BF548 |

| ADSP-BF506KSWZ-4F | IC DSP 12BIT 400MHZ 120LQFP |

| ADSP-BF518BSWZ-4F4 | IC DSP 16/32B 400MHZ LP 176LQFP |

| ADSP-BF526KBCZ-4C2 | IC DSP CTRLR 400MHZ 289CSPBGA |

| ADSP-BF535PKB-350 | IC DSP CONTROLLER 16BIT 260 BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21992YST | 制造商:Analog Devices 功能描述: |

| ADSP-21BT101JST | 制造商:Analog Devices 功能描述: |

| ADSP21CSP01BS200 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP21CSP01KS200 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP-21MOD810-000 | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。