参数资料

| 型号: | ADSP-3PARCBF548M01 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/100页 |

| 文件大小: | 0K |

| 描述: | MODULE BOARD BF548 |

| 产品培训模块: | Arcturus uCBF54x-EMM |

| 特色产品: | uCBF54x Start Kit and System Module by Arcturus |

| 标准包装: | 5 |

| 系列: | Blackfin® |

| 模块/板类型: | 处理器模块 |

| 适用于相关产品: | ADSP-BF548 |

| 相关产品: | ADSP-BF548MBBCZ-5M-ND - IC DSP 533MHZ W/DDR 400CSPBGA ADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

ADSP-BF542/ADSP-BF544/ADSP-BF547/ADSP-BF548/ADSP-BF549

Rev. C

|

Page 21 of 100

|

February 2010

sion 2.1. An I2C multiplexer can be used to select one

processor at a time when booting multiple processors from

a single TWI.

Boot from UART host (BMODE = 0x7)—In this mode, the

processor uses UART1 as the booting source. Using an

autobaud handshake sequence, a boot-stream-formatted

program is downloaded by the host. The host agent selects

a bit rate within the UART’s clocking capabilities.

When performing the autobaud, the UART expects an “@”

(0x40) character (eight data bits, one start bit, one stop bit,

no parity bit) on the UART1RX pin to determine the bit

rate. It then replies with an acknowledgement, which is

composed of four bytes (0xBF, the value of UART1_DLL,

the value of UART1_DLH, and finally 0x00). The host can

then download the boot stream. The processor deasserts

the UART1RTS output to hold off the host; UART1CTS

functionality is not enabled at boot time.

Boot from (DDR) SDRAM (BMODE = 0xA)—In this

mode, the boot kernel starts booting from address

0x0000 0010. This is a warm boot scenario only. The

SDRAM is expected to contain a valid boot stream and the

SDRAM controller must have been configured by the OTP

settings.

Boot from 8-bit and 16-bit external NAND flash memory

(BMODE = 0xD)—In this mode, auto detection of the

NAND flash device is performed. The processor configures

PORTJ GPIO pins PJ1 and PJ2 to enable the ND_CE and

ND_RB signals, respectively. For correct device operation,

pull-up resistors are required on both ND_CE (PJ1) and

ND_RB (PJ2) signals. By default, a value of 0x0033 is writ-

ten to the NFC_CTL register. The booting procedure

always starts by booting from byte 0 of block 0 of the

NAND flash device. In this boot mode, the HWAIT signal

does not toggle. The respective GPIO pin remains in the

high-impedance state.

NAND flash boot supports the following features:

Device auto detection

Error detection and correction for maximum

reliability

No boot stream size limitation

Peripheral DMA via channel 22, providing efficient

transfer of all data (excluding the ECC parity data)

Software-configurable boot mode for booting from

boot streams expanding multiple blocks, including

bad blocks

Software-configurable boot mode for booting from

multiple copies of the boot stream allowing for han-

dling of bad blocks and uncorrectable errors

Configurable timing via OTP memory

Small page NAND flash devices must have a 512-byte page

size, 32 pages per block, a 16-byte spare area size and a bus

configuration of eight bits. By default, all read requests

from the NAND flash are followed by four address cycles.

If the NAND flash device requires only three address

cycles, then the device must be capable of ignoring the

additional address cycle.

The small page NAND flash device must comply with the

following command set:

For large page NAND flash devices, the 4-byte electronic

signature is read in order to configure the kernel for boot-

ing. This allows support for multiple large page devices.

The fourth byte of the electronic signature must comply

with the specifications in Table 10.

Any configuration from Table 10 that also complies with

the command set listed below is directly supported by the

boot kernel. There are no restrictions on the page size or

block size as imposed by the small-page boot kernel.

Large page devices must support the following command set:

Large page devices must not support or react to NAND flash

command 0x50. This is a small page NAND flash command

used for device auto detection.

Reset: 0xFF

Read lower half of page: 0x00

Read upper half of page: 0x01

Read spare area: 0x50

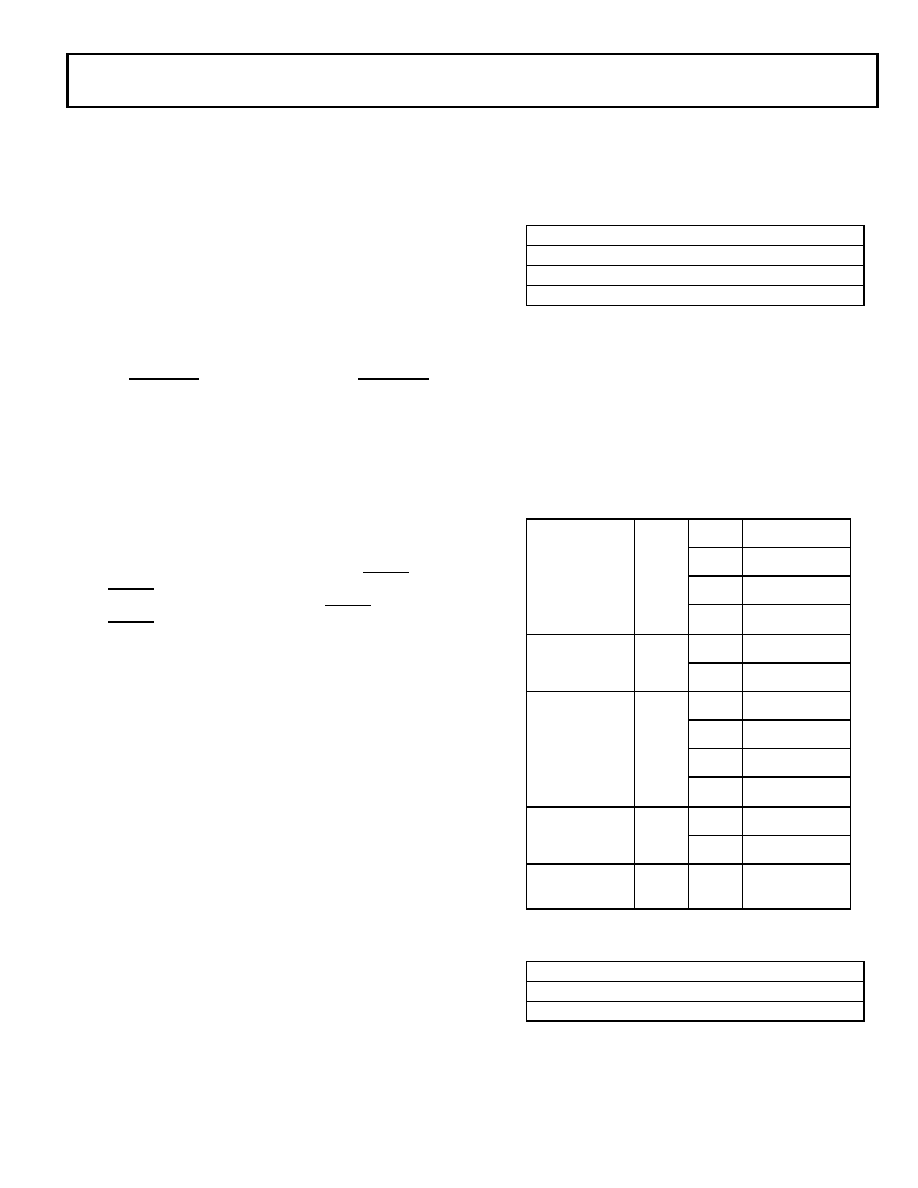

Table 10. Byte 4 Electronic Signature Specification

Page Size

(excluding spare

area)

D1:D0

00

1K bytes

01

2K bytes

10

4K bytes

11

8K bytes

Spare Area Size

D2

0

8 bytes/512 bytes

1

16 bytes/512 bytes

Block Size

(excluding spare

area)

D5:4

00

64K bytes

01

128K bytes

10

256K bytes

11

512K bytes

Bus Width

D6

0

x8

1x16

Not Used for

Configuration

D3, D7

Reset: 0xFF

Read Electronic Signature: 0x90

Read: 0x00, 0x30 (confirm command)

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-BF506KSWZ-4F | IC DSP 12BIT 400MHZ 120LQFP |

| ADSP-BF518BSWZ-4F4 | IC DSP 16/32B 400MHZ LP 176LQFP |

| ADSP-BF526KBCZ-4C2 | IC DSP CTRLR 400MHZ 289CSPBGA |

| ADSP-BF535PKB-350 | IC DSP CONTROLLER 16BIT 260 BGA |

| ADSP-BF538BBCZ-4A | IC DSP CTLR 16BIT 316CSPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF504BCPZ-3F | 功能描述:IC CCD SIGNAL PROCESSOR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF504BCPZ-4 | 功能描述:IC CCD SIGNAL PROCESSOR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-BF504BCPZ-4F | 功能描述:IC CCD SIGNAL PROCESSOR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF504KCPZ-3F | 功能描述:IC CCD SIGNAL PROCESSOR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-BF504KCPZ-4 | 功能描述:IC CCD SIGNAL PROCESSOR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。