- 您现在的位置:买卖IC网 > PDF目录12024 > AT89C51ID2-SLSUM (Atmel)IC 8051 MCU FLASH 64K 44PLCC PDF资料下载

参数资料

| 型号: | AT89C51ID2-SLSUM |

| 厂商: | Atmel |

| 文件页数: | 139/157页 |

| 文件大小: | 0K |

| 描述: | IC 8051 MCU FLASH 64K 44PLCC |

| 产品培训模块: | MCU Product Line Introduction |

| 标准包装: | 972 |

| 系列: | 89C |

| 核心处理器: | 8051 |

| 芯体尺寸: | 8-位 |

| 速度: | 60MHz |

| 连通性: | I²C,SPI,UART/USART |

| 外围设备: | POR,PWM,WDT |

| 输入/输出数: | 34 |

| 程序存储器容量: | 64KB(64K x 8) |

| 程序存储器类型: | 闪存 |

| EEPROM 大小: | 2K x 8 |

| RAM 容量: | 2K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2.7 V ~ 5.5 V |

| 振荡器型: | 外部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 44-LCC(J 形引线) |

| 包装: | 管件 |

| 配用: | AT89OCD-01-ND - USB EMULATOR FOR AT8XC51 MCU |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页当前第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页

82

AT89C51ID2

4289C–8051–11/05

Description

The CPU interfaces to the 2-wire logic via the following four 8-bit special function regis-

ters: the Synchronous Serial Control register (SSCON; Table 71), the Synchronous

Serial Data register (SSDAT; Table 72), the Synchronous Serial Control and Status reg-

ister (SSCS; Table 73) and the Synchronous Serial Address register (SSADR Table 76).

SSCON is used to enable the TWI interface, to program the bit rate (see Table 64), to

enable slave modes, to acknowledge or not a received data, to send a START or a

STOP condition on the 2-wire bus, and to acknowledge a serial interrupt. A hardware

reset disables the TWI module.

SSCS contains a status code which reflects the status of the 2-wire logic and the 2-wire

bus. The three least significant bits are always zero. The five most significant bits con-

tains the status code. There are 26 possible status codes. When SSCS contains F8h,

no relevant state information is available and no serial interrupt is requested. A valid sta-

tus code is available in SSCS one machine cycle after SI is set by hardware and is still

status for the master modes and miscellaneous states.

SSDAT contains a byte of serial data to be transmitted or a byte which has just been

received. It is addressable while it is not in process of shifting a byte. This occurs when

2-wire logic is in a defined state and the serial interrupt flag is set. Data in SSDAT

remains stable as long as SI is set. While data is being shifted out, data on the bus is

simultaneously shifted in; SSDAT always contains the last byte present on the bus.

SSADR may be loaded with the 7-bit slave address (7 most significant bits) to which the

TWI module will respond when programmed as a slave transmitter or receiver. The LSB

is used to enable general call address (00h) recognition.

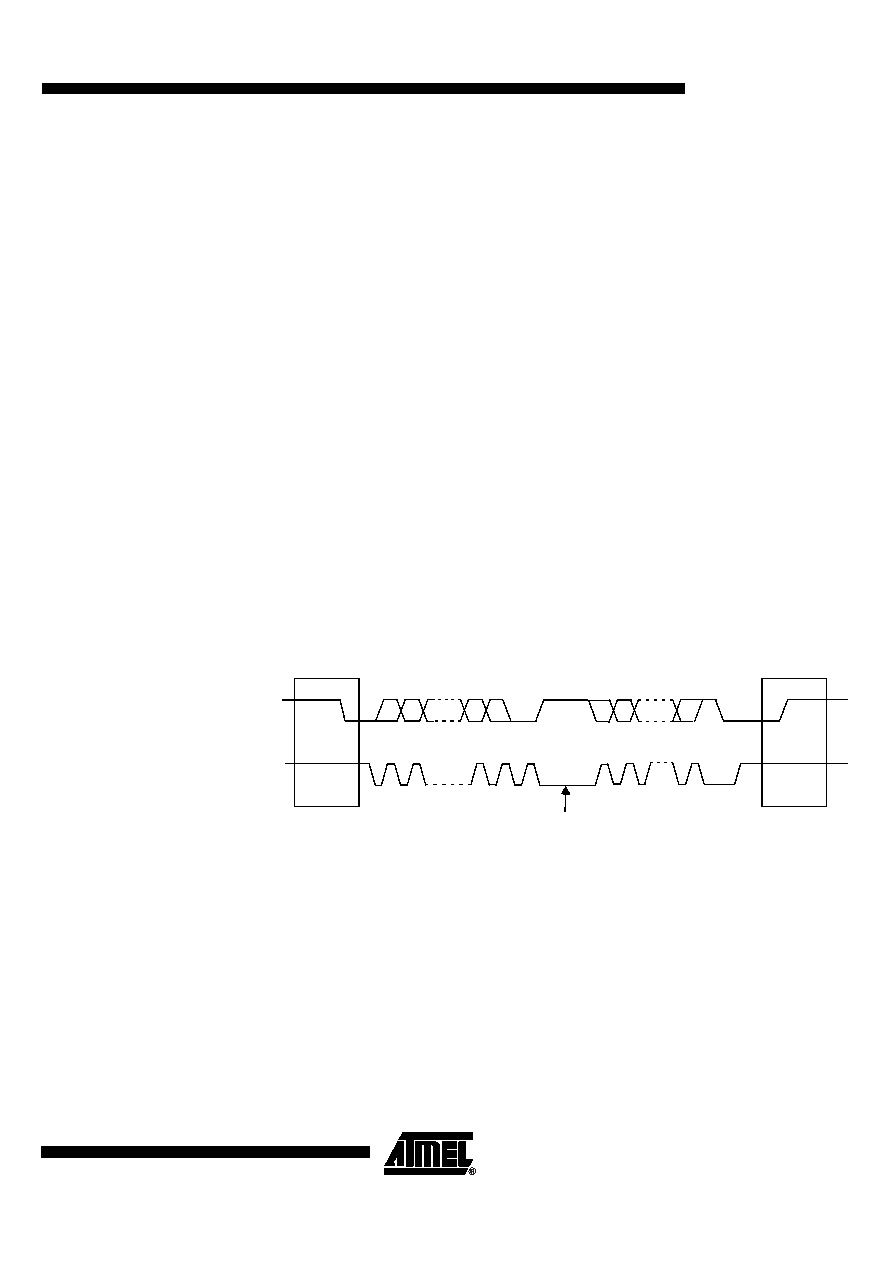

Figure 31 shows how a data transfer is accomplished on the 2-wire bus.

Figure 31. Complete Data Transfer on 2-wire Bus

The four operating modes are:

Master Transmitter

Master Receiver

Slave transmitter

Slave receiver

Figure 35.. These figures contain the following abbreviations:

S : START condition

R : Read bit (high level at SDA)

SDA

SCL

S

start

condition

MSB

12

7

89

ACK

acknowledgement

signal from receiver

acknowledgement

signal from receiver

12

3-8

9

ACK

stop

condition

P

clock line held low

while interrupts are serviced

相关PDF资料 |

PDF描述 |

|---|---|

| AT91SAM7X128B-CU | IC MCU 128KB FLASH 100TFBGA |

| AT91SAM7XC128B-AU | MCU ARM 128K HS FLASH 100-LQFP |

| ATSAM3U1CA-CU | IC MCU 32BIT 64KB FLASH 100TFBGA |

| 1981584-1 | CONN RCPT MICRO USB TYPE AB |

| 1981568-1 | CONN RCPT MICRO USB B R/A SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AT89C51ID2-SMSIM | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Flash Microcontroller |

| AT89C51ID2-UM | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Flash Microcontroller |

| AT89C51RB2 | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 16K/ 32K Bytes Flash |

| AT89C51RB2/RC2 | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:AT89C51RB2/RC2 [Updated 4/03. 125 Pages] |

| AT89C51RB2_06 | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 16K/ 32K Bytes Flash |

发布紧急采购,3分钟左右您将得到回复。