- 您现在的位置:买卖IC网 > PDF目录12052 > AT89LP3240-20PU (Atmel)MCU 8051 32K FLASH 20MHZ PDF资料下载

参数资料

| 型号: | AT89LP3240-20PU |

| 厂商: | Atmel |

| 文件页数: | 137/200页 |

| 文件大小: | 0K |

| 描述: | MCU 8051 32K FLASH 20MHZ |

| 标准包装: | 10 |

| 系列: | 89LP |

| 核心处理器: | 8051 |

| 芯体尺寸: | 8-位 |

| 速度: | 20MHz |

| 连通性: | I²C,SPI,UART/USART |

| 外围设备: | 欠压检测/复位,POR,PWM,WDT |

| 输入/输出数: | 38 |

| 程序存储器容量: | 32KB(32K x 8) |

| 程序存储器类型: | 闪存 |

| EEPROM 大小: | 8K x 8 |

| RAM 容量: | 4.25K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2.4 V ~ 3.6 V |

| 数据转换器: | A/D 8x10b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 40-DIP(0.540",13.72mm) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页当前第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页

41

3706C–MICRO–2/11

AT89LP3240/6440

9.1

Interrupt Response Time

The interrupt flags may be set by their hardware in any clock cycle. The interrupt controller polls

the flags in the last clock cycle of the instruction in progress. If one of the flags was set in the

preceding cycle, the polling cycle will find it and the interrupt system will generate an LCALL to

the appropriate service routine as the next instruction, provided that the interrupt is not blocked

by any of the following conditions: an interrupt of equal or higher priority level is already in prog-

ress; the instruction in progress is RETI or any write to the IE, IP, IPH, IE2, IP2 or IP2H registers;

the CPU is currently forced into idle by an IAP or FDATA write. Each of these conditions will

block the generation of the LCALL to the interrupt service routine. The second condition ensures

that if the instruction in progress is RETI or any access to IE, IP, IPH, IE2, IP2 or IP2H, then at

least one more instruction will be executed before any interrupt is vectored to. The polling cycle

is repeated at the last cycle of each instruction, and the values polled are the values that were

present at the previous clock cycle. If an active interrupt flag is not being serviced because of

one of the above conditions and is no longer active when the blocking condition is removed, the

denied interrupt will not be serviced. In other words, the fact that the interrupt flag was once

active but not serviced is not remembered. Every polling cycle is new.

If a request is active and conditions are met for it to be acknowledged, a hardware subroutine

call to the requested service routine will be the next instruction executed. The call itself takes

four cycles. Thus, a minimum of five complete clock cycles elapsed between activation of an

interrupt request and the beginning of execution of the first instruction of the service routine. A

longer response time results if the request is blocked by one of the previously listed conditions. If

an interrupt of equal or higher priority level is already in progress, the additional wait time

depends on the nature of the other interrupt's service routine. If the instruction in progress is not

in its final clock cycle, the additional wait time cannot be more than 8 cycles, since the longest

instruction is 9 cycles long. If the instruction in progress is RETI with XSTK, the additional wait

time cannot be more than 14 cycles (a maximum of 5 more cycles to complete the instruction in

progress, plus a maximum of 9 cycles to complete the next instruction). Thus, in a single-inter-

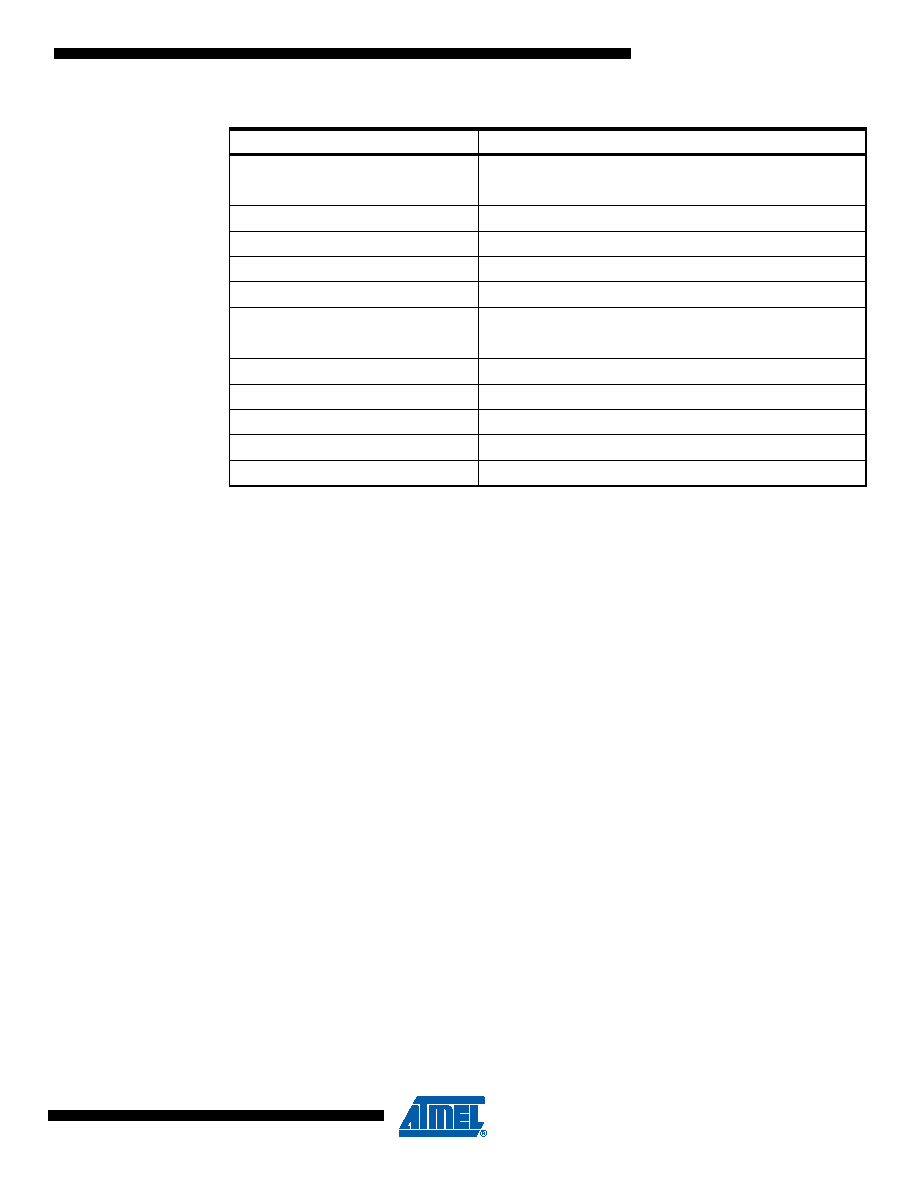

Table 9-1.

Interrupt Vector Addresses

Interrupt

Source

Vector Address

System Reset

RST or POR or BOD

0000H

External Interrupt 0

IE0

0003H

Timer 0 Overflow

TF0

000BH

External Interrupt 1

IE1

0013H

Timer 1 Overflow

TF1

001BH

Serial Port Interrupt

RI or TI

0023H

Timer 2 Interrupt

TF2 or EXF2

002BH

Analog Comparator Interrupt

CFA or CFB

0033H

General-purpose Interrupt

GPIF

7-0

003BH

Compare/Capture Array Interrupt

T2CCF3-0

0043H

Serial Peripheral Interface Interrupt

SPIF or MODF or TXE

004BH

ADC Interrupt

ADIF

0053H

Two-Wire Interface Interrupt

TWIF

005BH

相关PDF资料 |

PDF描述 |

|---|---|

| VI-JTZ-IY-F4 | CONVERTER MOD DC/DC 2V 20W |

| VI-JTZ-IY-F2 | CONVERTER MOD DC/DC 2V 20W |

| ATMEGA164A-PU | IC MCU AVR 16K 20MHZ 40PDIP |

| VI-J0J-IX-B1 | CONVERTER MOD DC/DC 36V 75W |

| VI-JTZ-IY-F1 | CONVERTER MOD DC/DC 2V 20W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AT89LP4052-16PI | 功能描述:8位微控制器 -MCU Microcontroller RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| AT89LP4052-16PU | 功能描述:8位微控制器 -MCU Microcontroller RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| AT89LP4052-16SI | 功能描述:8位微控制器 -MCU Microcontroller RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| AT89LP4052-16SU | 功能描述:IC 8051 MCU FLASH 4K 20SOIC RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:89LP 标准包装:1,500 系列:AVR® ATtiny 核心处理器:AVR 芯体尺寸:8-位 速度:16MHz 连通性:I²C,LIN,SPI,UART/USART,USI 外围设备:欠压检测/复位,POR,PWM,温度传感器,WDT 输入/输出数:16 程序存储器容量:8KB(4K x 16) 程序存储器类型:闪存 EEPROM 大小:512 x 8 RAM 容量:512 x 8 电压 - 电源 (Vcc/Vdd):2.7 V ~ 5.5 V 数据转换器:A/D 11x10b 振荡器型:内部 工作温度:-40°C ~ 125°C 封装/外壳:20-SOIC(0.295",7.50mm 宽) 包装:带卷 (TR) |

| AT89LP4052-16XI | 功能描述:8位微控制器 -MCU Microcontroller RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。