- 您现在的位置:买卖IC网 > PDF目录298892 > BX80547RE2933CN (INTEL CORP) 32-BIT, 2930 MHz, MICROPROCESSOR, PBGA775 PDF资料下载

参数资料

| 型号: | BX80547RE2933CN |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 2930 MHz, MICROPROCESSOR, PBGA775 |

| 封装: | FLIP CHIP, LGA-775 |

| 文件页数: | 14/94页 |

| 文件大小: | 2796K |

| 代理商: | BX80547RE2933CN |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页

Datasheet

21

Electrical Specifications

With the implementation of a source synchronous data bus comes the need to specify two sets of

timing parameters. One set is for common clock signals which are dependent upon the rising edge

of BCLK0 (ADS#, HIT#, HITM#, etc.) and the second set is for the source synchronous signals

which are relative to their respective strobe lines (data and address) as well as the rising edge of

BCLK0. Asychronous signals are still present (A20M#, IGNNE#, etc.) and can become active at

any time during the clock cycle. Table 2-3 identifies which signals are common clock, source

synchronous, and asynchronous.

NOTES:

1. Refer to Section 4.2 for signal descriptions.

2. EDRDY# and PC_REQ# are not features of the Celeron D processor in the 775-land package. They are

included here for future processor compatibility.

3. The value of these signals during the active-to-inactive edge of RESET# defines the processor configuration

options. See Section 6.1 for details.

4. PC_REQ# is driven by the processor as Common Clock (1X); however, it must be received at the chipset as

Source Synchronous and associated with ADSTB0#.

5. In processor systems where there is no debug port implemented on the system board, these signals are used

to support a debug port interposer. In systems with the debug port implemented on the system board, these

signals are no connects.

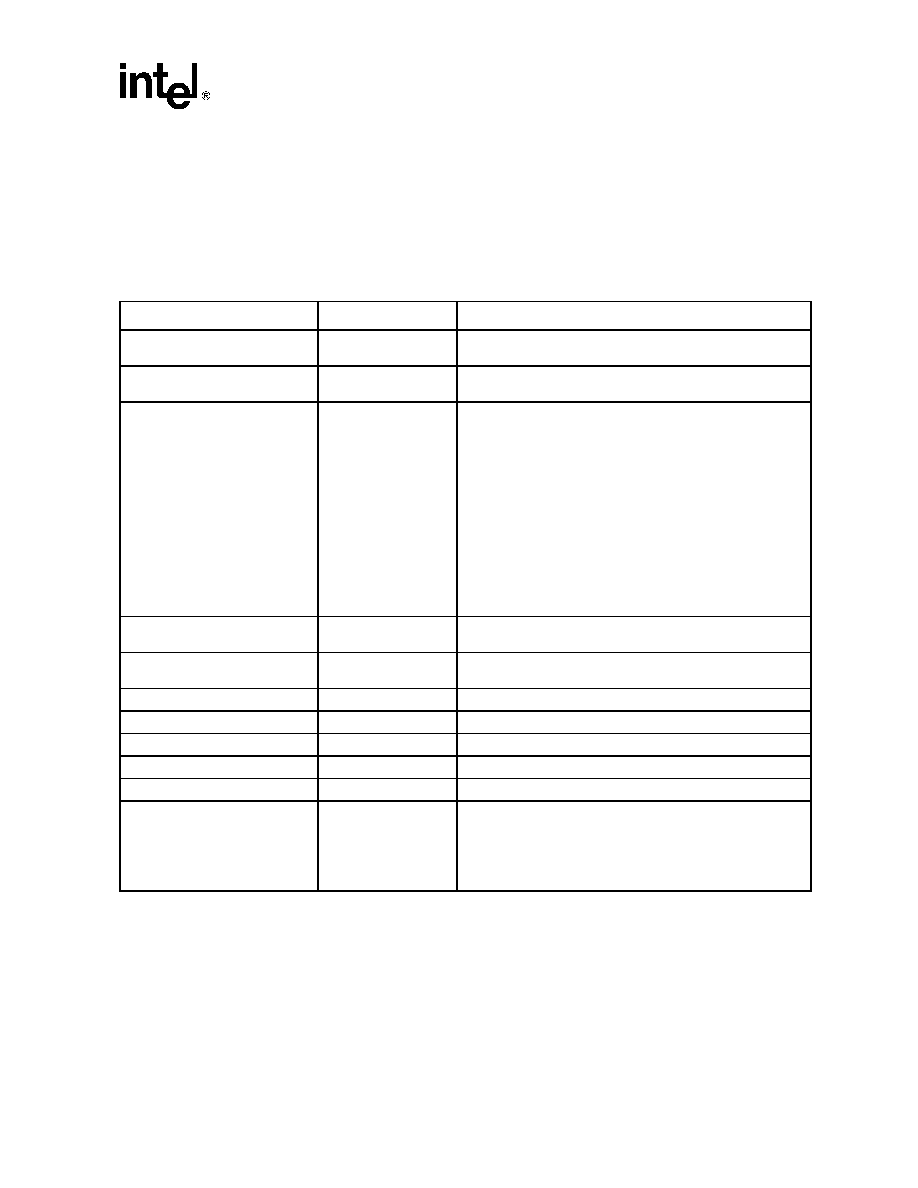

Table 2-3. FSB Signal Groups

Signal Group

Type

Signals1

GTL+ Common Clock Input

Synchronous to

BCLK[1:0]

BPRI#, DEFER#, RS[2:0]#, RSP#, TRDY#, EDRDY#2

GTL+ Common Clock I/O

Synchronous to

BCLK[1:0]

AP[1:0]#, ADS#, BINIT#, BNR#, BPM[5:0]#, BR0#, DBSY#,

DP[3:0]#, DRDY#, HIT#, HITM#, LOCK#, MCERR#

GTL+ Source Synchronous I/O

Synchronous to assoc.

strobe

GTL+ Strobes

Synchronous to

BCLK[1:0]

ADSTB[1:0]#, DSTBP[3:0]#, DSTBN[3:0]#

GTL+ Asynchronous Input

A20M#, IGNNE#, INIT#, LINT0/INTR, LINT1/NMI, SMI#,

STPCLK#, RESET#

GTL+ Asynchronous Output

FERR#/PBE#, IERR#, THERMTRIP#

GTL+ Asynchronous Input/Output

PROCHOT#

TAP Input

Synchronous to TCK

TCK, TDI, TMS, TRST#

TAP Output

Synchronous to TCK

TDO

FSB Clock

Clock

BCLK[1:0], ITP_CLK[1:0]5

Power/Other

VCC, VTT, VCCA, VCCIOPLL, VID[7:0], VSS, VSSA,

GTLREF[1:0], COMP[5:0], RESERVED, TESTHI[13:0],

THERMDA, THERMDC, VCC_SENSE, VSS_SENSE,

BSEL[2:0], SKTOCC#, DBR#5, VTTPWRGD, BOOTSELECT,

PWRGOOD, VTT_OUT_LEFT, VTT_OUT_RIGHT, VTT_SEL,

LL_ID[1:0], VID_SELECT, GTLREF_SEL

Signals

Associated Strobe

REQ[4:0]#, A[16:3]#3

PC_REQ#2, 4

ADSTB0#

A[35:17]#3

ADSTB1#

D[15:0]#, DBI0#

DSTBP0#, DSTBN0#

D[31:16]#, DBI1#

DSTBP1#, DSTBN1#

D[47:32]#, DBI2#

DSTBP2#, DSTBN2#

D[63:48]#, DBI3#

DSTBP3#, DSTBN3#

相关PDF资料 |

PDF描述 |

|---|---|

| BX80551PG2800FN | 32-BIT, 2800 MHz, MICROPROCESSOR, PBGA775 |

| BX80551PG2800FT | 32-BIT, 2800 MHz, MICROPROCESSOR, PBGA775 |

| BX80552360 | 32-BIT, 3460 MHz, MICROPROCESSOR, CBGA775 |

| BX80552651 | 32-BIT, 3400 MHz, MICROPROCESSOR, PBGA775 |

| BX80552651T | 32-BIT, 3400 MHz, MICROPROCESSOR, PBGA775 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BX80547RE2933CNS L98X | 制造商:Intel 功能描述:32BIT MPU BX80547RE2933CN 2.93 |

| BX805499010 | 制造商:Intel 功能描述:ITANIUM 1.60 GHZ - Boxed Product (Development Kits) |

| BX805499015 | 制造商:Intel 功能描述:DUAL-CORE ITANIUM 1.40 GHZ - Boxed Product (Development Kits) |

| BX805499020 | 制造商:Intel 功能描述:DUAL-CORE ITANIUM 1.42 GHZ - Boxed Product (Development Kits) |

| BX805499030 | 制造商:Intel 功能描述:DUAL-CORE ITANIUM 1.60 GHZ - Boxed Product (Development Kits) |

发布紧急采购,3分钟左右您将得到回复。