参数资料

| 型号: | CDP68HC68T1MZ96 |

| 厂商: | Intersil |

| 文件页数: | 3/23页 |

| 文件大小: | 0K |

| 描述: | IC RTC RAM/SPI SERIAL 20-SOIC |

| 标准包装: | 1,000 |

| 类型: | 时钟/日历 |

| 特点: | 警报器,闰年,方波输出,监视计时器 |

| 存储容量: | 32B |

| 时间格式: | HH:MM:SS(12/24 小时) |

| 数据格式: | YY-MM-DD-dd |

| 接口: | SPI |

| 电源电压: | 3 V ~ 6 V |

| 电压 - 电源,电池: | 2.2 V ~ 6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 20-SOIC W |

| 包装: | 带卷 (TR) |

11

FN1547.8

October 29, 2007

VSYS

This input is connected to the system voltage. After the CPU

initiates power down by setting Bit 6 in the Interrupt Control

Register to “1”, the level on this pin will terminate power

down if it rises about 1.0V above the level at the VBATT input

pin after previously falling below VBATT +1.0V. When

power-down is terminated, the PSE pin will return high and

the Clock Output will be enabled. The CPUR output pin will

also return high. The logic level present at this pin at the end

of POR determines the CDP68HC68T1’s operating mode.

VBATT

The oscillator power source. The positive terminal of the

battery should be connected to this pin. When the level on

the VSYS pin falls below VBATT +1.0V, the VBATT pin will be

internally connected to the VDD pin. When the voltage on

VSYS rises a threshold above (1.0V) the voltage on VBATT,

the connection from VBATT to the VDD pin is opened. When

the “LINE” input is used as the frequency source, VBATT

may be tied to VDD or VSS. The “XTAL IN” pin must be at

VSS if VBATT is at VSS. If VBATT is connected to VDD, the

“XTAL IN” pin can be tied to VSS or VDD.

XTAL IN, XTAL OUT

These pins are connected to a 32,768Hz. 1.048576MHz,

2.097152MHz or 4.194304MHz crystal. If an external clock

is used, it should be connected to “XTAL IN” with ‘XTAL

OUT” left open.

VDD

The positive power-supply pin.

Clock Control Register

Start-Stop

A high written into this bit will enable the counter stages of

the clock circuitry. A low will hold all bits reset in the divider

chain from 32Hz to 1Hz. A clock out selected by Bit 0, Bit 1

and Bit 2 will not be affected by the stop function except the

1Hz and 2Hz outputs.

Line-XTAL

When this bit is set high, clock operation will use the

50-cycle or 60-cycle input present at the LINE input pin.

When the bit is low, the crystal input will generate the 1Hz

time update.

XTAL Select

One of 4 possible crystals is selected by value in these two

bits:

0 = 4.194304MHz

2 = 1.048576MHz

1 = 2.097152MHz

3 = 32,768Hz

50Hz to 60Hz

50Hz is selected as the line input frequency when this bit is

set high. A low will select 60Hz. The power-sense bit in the

Interrupt Control Register must be set low for line frequency

operation.

Clock Out

The three bits specify one of the 7 frequencies to be used as

the squarewave clock output:

0 = XTAL

4 = Disable (low output)

1 = XTAL/2

5 = 1Hz

2 = XTAL/4

6 = 2Hz

3 = XTAL/8

7 = 50Hz or 60Hz

XTAL Operation = 64Hz

All bits are reset by a power-on reset. Therefore, the XTAL is

selected as the clock output at this time.

Interrupt Control Register

Watchdog

When this bit is set high, the watchdog operation will be

enabled. This function requires the CPU to toggle the CE pin

periodically without a serial-transfer requirement. In the

event this does not occur, a CPU reset will be issued. Status

Register must be read before re-enabling watchdog.

Power-Down

A high in this location will initiate a power down. A CPU reset

will occur, the CLK OUT and PSE output pins will be set low

and the serial interface will be disabled.

Power Sense

This bit is used to enable the line input pin to sense a power

failure. It is set high for this function. When power sense is

selected, the input to the 50Hz to 60Hz prescaler is

disconnected. Therefore, crystal operation is required when

power sense is enabled. An interrupt is generated when a

power failure is sensed and the power sense and Interrupt

True bit in the Status Register are set. When power sense is

activated, a “0” must be written to this location followed by a

“1” to re-enable power sense.

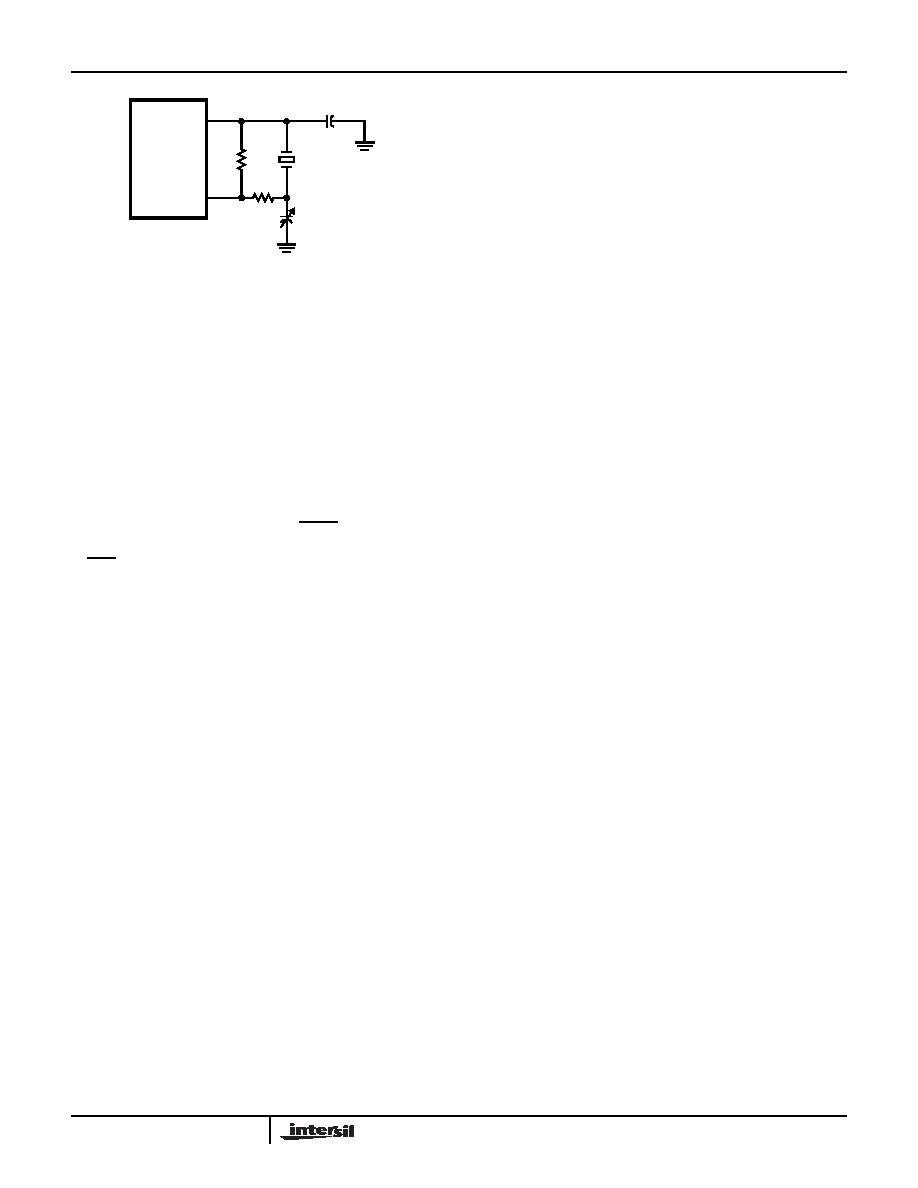

XTAL

IN

22M

T1

XTAL

OUT

R

(

N

OTE

8)

CR

YST

AL

C2

10pF TO 40pF

C1

5pF TO 30pF

NOTES:

7. All frequencies recommended oscillator circuit. C1, C2 values

crystal dependent.

8. R is used for 32KHz operation only. 100k to 300k range as

specified by crystal manufacturer.

FIGURE 7. OSCILLATOR CIRCUIT

CDP68HC68T1

相关PDF资料 |

PDF描述 |

|---|---|

| ISL23318WFRUZ-T7A | IC DGTL POT 1CH 10K 10UTQFN |

| ISL12020MIRZ-T | IC RTC/CALENDAR TEMP SNSR 20-DFN |

| VI-BNK-MV | CONVERTER MOD DC/DC 40V 150W |

| ISL12029IV27AZ | IC RTC/CALENDAR EEPROM 14-TSSOP |

| ISL12022MIBZ-TR5421 | IC RTC/CALENDAR TEMP SNSR 20SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDP68HC68T1W | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS Serial Real-Time Clock With RAM and Power Sense/Control |

| CDP68HC68T1W WAF | 制造商:Harris Corporation 功能描述: |

| CDP68HC68T2D | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Real-Time Clock |

| CDP68HC68T2E | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Real-Time Clock |

| CDP68HC68T2M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Real-Time Clock |

发布紧急采购,3分钟左右您将得到回复。