- 您现在的位置:买卖IC网 > Datasheet目录319 > COP8SG-EPU (National Semiconductor)BOARD PROTOTYPE/TARGET COP8 Datasheet资料下载

参数资料

| 型号: | COP8SG-EPU |

| 厂商: | National Semiconductor |

| 文件页数: | 27/55页 |

| 文件大小: | 0K |

| 描述: | BOARD PROTOTYPE/TARGET COP8 |

| 标准包装: | 1 |

| 系列: | COP8™ |

| 类型: | MCU |

| 适用于相关产品: | Cop 8 |

| 所含物品: | 板 |

| 相关产品: | COP8SGR728M7-ND - MCU 8BIT CMOS ROM OTP 28-SOIC COP8SGR744V8-ND - IC MCU 8BIT CMOS OTP 44PLCC COP8SGR728N8/NOPB-ND - IC MCU 8BIT CMOS OTP 28DIP COP8SGR728M8-ND - IC MCU 8BIT CMOS OTP 28SOIC COP8SGE7VEJ8-ND - IC MCU 8BIT CMOS OTP 44LQFP COP8SGE744V8/NOPB-ND - IC MCU 8BIT CMOS OTP 44PLCC COP8SGE728N8-ND - IC MCU 8BIT CMOS OTP 28DIP COP8SGE728M8/NOPB-ND - IC MCU 8BIT CMOS OTP 28SOIC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页

�� �

�

USART�

�(Continued)�

�RCVG:� This� bit� is� set� high� whenever� a� framing� error� occurs�

�and� goes� low� when� RDX� goes� high.� Read� only,� cleared� on�

�CHL1,� CHL0:� These� bits� select� the� character� frame� format.�

�Parity� is� not� included� and� is� generated/verified� by� hardware.�

�Read/Write,� cleared� on� reset.�

�CHL1� =� 0,� CHL0� =� 0� The� frame� contains� eight� data� bits.�

�reset.�

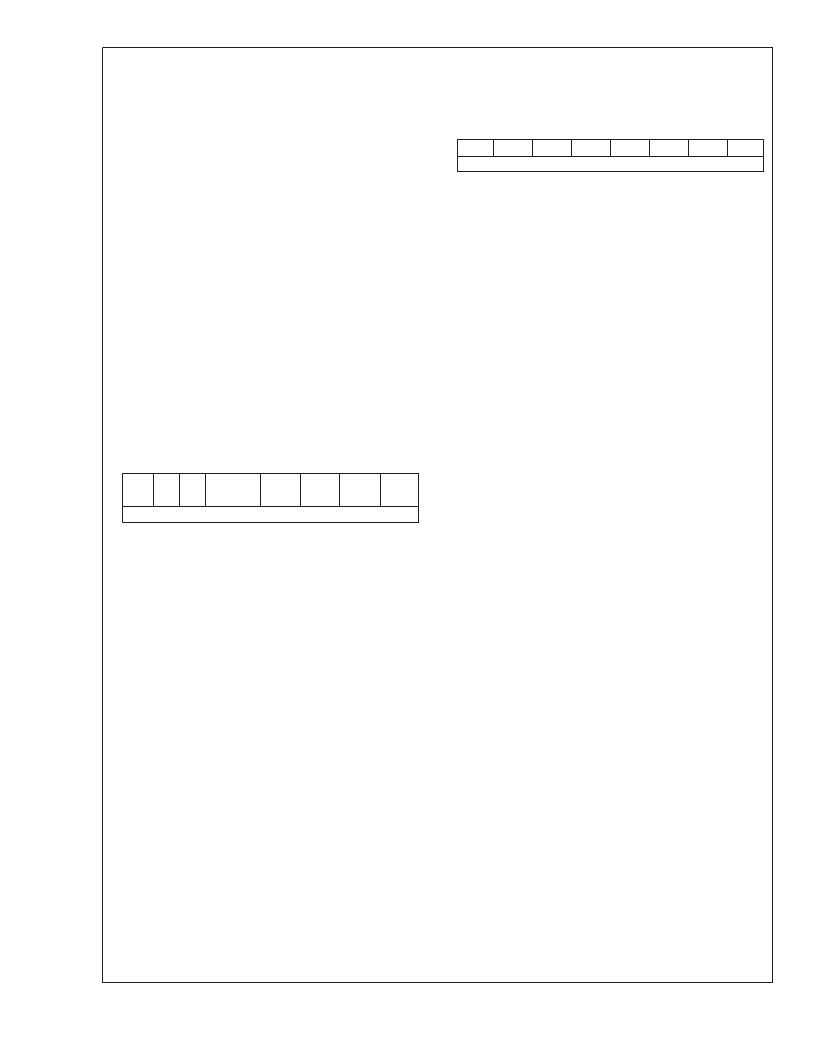

�ENUI-USART� Interrupt� and� Clock� Source� Register�

�(Address� at� 0BC)�

�CHL1� =� 0,� CHL0� =� 1�

�The� frame� contains� seven� data�

�STP2�

�STP78�

�ETDX�

�SSEL� XRCLK� XTCLK�

�ERI�

�ETI�

�bits.�

�Bit� 7�

�Bit� 0�

�CHL1� =� 1,� CHL0� =� 0� The� frame� contains� nine� data� bits.�

�CHL1� =� 1,� CHL0� =� 1� Loopback� Mode� selected.� Trans-�

�mitter� output� internally� looped� back�

�to� receiver� input.� Nine� bit� framing�

�format� is� used.�

�ERR:� This� bit� is� a� global� USART� error� flag� which� gets� set� if�

�any� or� a� combination� of� the� errors� (DOE,� FE,� PE)� occur.�

�Read� only;� it� cannot� be� written� by� software,� cleared� on� reset.�

�RBFL:� This� bit� is� set� when� the� USART� has� received� a� com-�

�plete� character� and� has� copied� it� into� the� RBUF� register.� It� is�

�automatically� reset� when� software� reads� the� character� from�

�RBUF.� Read� only;� it� cannot� be� written� by� software,� cleared�

�on� reset.�

�TBMT:� This� bit� is� set� when� the� USART� transfers� a� byte� of�

�data� from� the� TBUF� register� into� the� TSFT� register� for� trans-�

�mission.� It� is� automatically� reset� when� software� writes� into�

�the� TBUF� register.� Read� only,� bit� is� set� to� “one”� on� reset;� it�

�cannot� be� written� by� software.�

�ENUR-USART� Receive� Control� and� Status� Register�

�(Address� at� 0BB)�

�STP2:� This� bit� programs� the� number� of� Stop� bits� to� be� trans-�

�mitted.� Read/Write,� cleared� on� reset.�

�STP2� =� 0� One� Stop� bit� transmitted.�

�STP2� =� 1� Two� Stop� bits� transmitted.�

�STP78:� This� bit� is� set� to� program� the� last� Stop� bit� to� be� 7/8th�

�of� a� bit� in� length.� Read/Write,� cleared� on� reset.�

�ETDX:� TDX� (USART� Transmit� Pin)� is� the� alternate� function�

�assigned� to� Port� L� pin� L2;� it� is� selected� by� setting� ETDX� bit.�

�To� simulate� line� break� generation,� software� should� reset�

�ETDX� bit� and� output� logic� zero� to� TDX� pin� through� Port� L�

�data� and� configuration� registers.� Read/Write,� cleared� on� re-�

�set.�

�SSEL:� USART� mode� select.� Read/Write,� cleared� on� reset.�

�SSEL� =� 0� Asynchronous� Mode.�

�SSEL� =� 1� Synchronous� Mode.�

�XRCLK:� This� bit� selects� the� clock� source� for� the� receiver�

�section.� Read/Write,� cleared� on� reset.�

�XRCLK� =� 0� The� clock� source� is� selected� through� the�

�PSR� and� BAUD� registers.�

�XRCLK� =� 1� Signal� on� CKX� (L1)� pin� is� used� as� the� clock.�

�DOE�

�FE�

�PE�

�Reserved�

�RBIT9�

�ATTN�

�XMTG�

�RCVG�

�XTCLK:� This� bit� selects� the� clock� source� for� the� transmitter�

�(Note� 12)�

�section.� Read/Write,� cleared� on� reset.�

�Bit� 7�

�Bit� 0�

�XTCLK� =� 0� The� clock� source� is� selected� through� the�

�Note� 12:� Bit� is� reserved� for� future� use.� User� must� set� to� zero.�

�DOE:� Flags� a� Data� Overrun� Error.� Read� only,� cleared� on�

�read,� cleared� on� reset.�

�DOE� =� 0� Indicates� no� Data� Overrun� Error� has� been� de-�

�tected� since� the� last� time� the� ENUR� register�

�was� read.�

�DOE� =� 1� Indicates� the� occurrence� of� a� Data� Overrun� Er-�

�ror.�

�FE:� Flags� a� Framing� Error.� Read� only,� cleared� on� read,�

�cleared� on� reset.�

�FE� =� 0� Indicates� no� Framing� Error� has� been� detected�

�since� the� last� time� the� ENUR� register� was� read.�

�FE� =� 1� Indicates� the� occurrence� of� a� Framing� Error.�

�PE:� Flags� a� Parity� Error.� Read� only,� cleared� on� read,� cleared�

�on� reset.�

�PE� =� 0� Indicates� no� Parity� Error� has� been� detected� since�

�the� last� time� the� ENUR� register� was� read.�

�PE� =� 1� Indicates� the� occurrence� of� a� Parity� Error.�

�SPARE:� Reserved� for� future� use.� Read/Write,� cleared� on� re-�

�set.�

�RBIT9:� Contains� the� ninth� data� bit� received� when� the� US-�

�ART� is� operating� with� nine� data� bits� per� frame.� Read� only,�

�cleared� on� reset.�

�ATTN:� ATTENTION� Mode� is� enabled� while� this� bit� is� set.�

�This� bit� is� cleared� automatically� on� receiving� a� character� with�

�data� bit� nine� set.� Read/Write,� cleared� on� reset.�

�XMTG:� This� bit� is� set� to� indicate� that� the� USART� is� transmit-�

�ting.� It� gets� reset� at� the� end� of� the� last� frame� (end� of� last� Stop�

�bit).� Read� only,� cleared� on� reset.�

�www.national.com�

�26�

�PSR� and� BAUD� registers.�

�XTCLK� =� 1� Signal� on� CKX� (L1)� pin� is� used� as� the� clock.�

�ERI:� This� bit� enables/disables� interrupt� from� the� receiver�

�section.� Read/Write,� cleared� on� reset.�

�ERI� =� 0� Interrupt� from� the� receiver� is� disabled.�

�ERI� =� 1� Interrupt� from� the� receiver� is� enabled.�

�ETI:� This� bit� enables/disables� interrupt� from� the� transmitter�

�section.� Read/Write,� cleared� on� reset.�

�ETI� =� 0� Interrupt� from� the� transmitter� is� disabled.�

�ETI� =� 1� Interrupt� from� the� transmitter� is� enabled.�

�Associated� I/O� Pins�

�Data� is� transmitted� on� the� TDX� pin� and� received� on� the� RDX�

�pin.� TDX� is� the� alternate� function� assigned� to� Port� L� pin� L2;�

�it� is� selected� by� setting� ETDX� (in� the� ENUI� register)� to� one.�

�RDX� is� an� inherent� function� of� Port� L� pin� L3,� requiring� no�

�setup.�

�The� baud� rate� clock� for� the� USART� can� be� generated�

�on-chip,� or� can� be� taken� from� an� external� source.� Port� L� pin�

�L1� (CKX)� is� the� external� clock� I/O� pin.� The� CKX� pin� can� be�

�either� an� input� or� an� output,� as� determined� by� Port� L� Con-�

�figuration� and� Data� registers� (Bit� 1).� As� an� input,� it� accepts� a�

�clock� signal� which� may� be� selected� to� drive� the� transmitter�

�and/or� receiver.� As� an� output,� it� presents� the� internal� Baud�

�Rate� Generator� output.�

�相关PDF资料 |

PDF描述 |

|---|---|

| CORE1553-DEV-KIT | KIT DEVELOPMENT FOR IP CORE1553 |

| CP131-AG | LNR PWR SUP 5V 8A, +/-12V 1.7A |

| CPC1590P | MOSFET GATE DVR ISO 8-FLATPACK |

| CPC5002G | ISOLAT DGTL 3.75KVRMS 2CH 8-DIP |

| CPCI-D-3U-300C | PWR SUPLY DC/DC CPCI 300W 3UX8HP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| COP8SGR728M7 | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| COP8SGR728M7/NOPB | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| COP8SGR728M8 | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| COP8SGR728M8/NOPB | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| COP8SGR728N8 | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。