参数资料

| 型号: | CS5376A-IQZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 45/49页 |

| 文件大小: | 0K |

| 描述: | IC FILTER DGTL MULTI-CH 64-TQFP |

| 标准包装: | 160 |

| 滤波器类型: | 数字 |

| 滤波器数: | 4 |

| 滤波器阶数: | 2nd |

| 电源电压: | 3 V ~ 5 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-TQFP(10x10) |

| 包装: | 管件 |

| 配用: | 598-1778-ND - EVALUATION BOARD FOR CS5376 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页当前第45页第46页第47页第48页第49页

2008 Fairchild Semiconductor Corporation

www.fairchildsemi.com

FUSB2805 Rev. 1.0.3

5

F

USB2

8

0

5

—

USB2

.0

High

-S

pee

d

OTG

Tra

nsc

e

iv

e

rw

ith

UL

P

I

Inter

fac

e

CLOCK

Chip_Select_N

STP

D[7:0]

NXT

3-State (input)

t

PWRDN

3-State (input)

3-State (ignored)

DIR

3-State

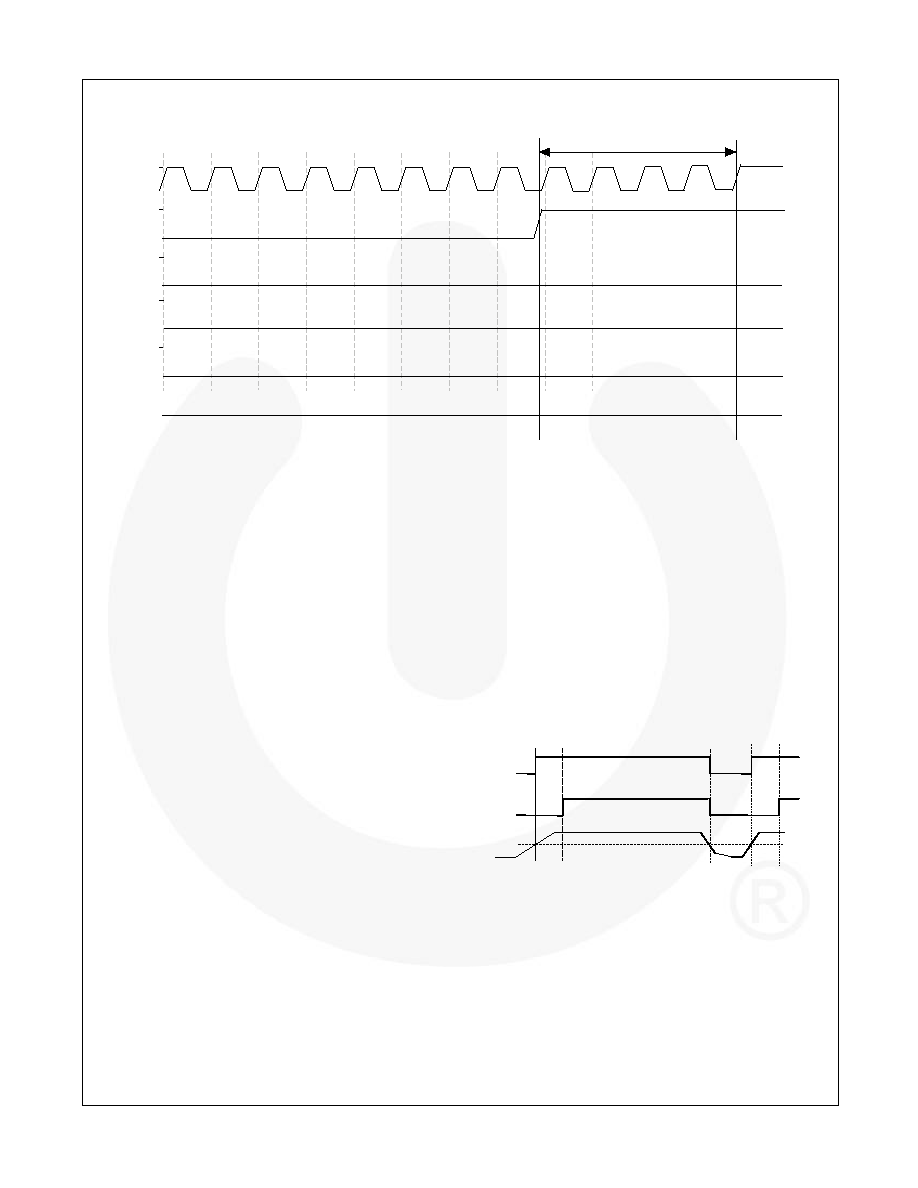

Figure 3. ULPI Behavior with Chip_Select_N as a Power-Down Control Signal

Power Down Using Chip_Select

When CHIP SELECT_N is de-asserted (HIGH), the

FUSB2805 three-states the ULPI interface pins and

powers

down

the

internal

circuitry.

If

CHIP

SELECT_N is not used as a power-down control

signal, it is tied to a LOW. Figure 3 shows the ULPI

interface

behavior

when

CHIP

SELECT_N

is

asserted and subsequently de-asserted.

After the tPWRDN duration, the CLOCK output enters

three-state and is ignored by the link.

Power-On Reset (POR)

The power supply for the internal regulators is VCC. This

supply is fed into the 3.3 V and 1.2 V regulators. The

output of the 3.3 V regulator is VCC3V3. The 1.2 V

regulator generates VDD1V2.

During the power-up stage, the POR is held in a stable

state to ensure that the digital logic does not operate

the I/O or any analog circuit in such a way that may be

damaging to the rest of the system.

The output of the POR block, PORB (internal signal),

should be 1b0 during the power supply ramping period.

Once the power supplies have completely ramped,

PORB should be de-asserted. This signal is driven into

the 19.2 / 26 MHz to 12 MHz PLL. The POR signal

(active HIGH reset) in the USB OTG PHY block must

remain asserted for no less than 40 s.

PORB de-assertion is determined via a comparator on

VCC3V3 with a POR trigger threshold, VPOR, of 2.0 V.

Figure 4 illustrates how PORB should be pulsed based

on the voltage level of VCC3V3. This diagram also shows

what the POR should do to PORB when VCC3V3 drops

below VPOR for any length of time.

When CLOCK starts toggling after power up, the USB

link controller must issue a reset command over the

ULPI bus to ensure correct operation.

PORB /

PLL

Reset

VCC3V3

VPOR

T0

T1

VCC3V3 = 3.3V

T1 = T0 + 40s

VPOR = 2.2V

T2

T3

T4

PHY POR

T4 = T3 + 40s

Figure 4. Power-On Reset Sequence

相关PDF资料 |

PDF描述 |

|---|---|

| CS61577-IL1Z | IC LINE INTERFACE T1/E1 28PLCC |

| CS61584A-IQ3Z | IC LINE INTERFACE T1/E1 64LQFP |

| CS61884-IRZ | IC LN INTERF T1/E1/J1 160-LFBGA |

| CS8130-CS | IC IR TRANSCEIVER 2-5V 20-SSOP |

| CS8190EDWF20G | IC TACH/SPEEDO DRVR PREC 20SOICW |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5376A-IQZR | 功能描述:特殊用途放大器 LP Multi-Ch. Decimation Filter RoHS:否 制造商:Texas Instruments 通道数量:Single 共模抑制比(最小值): 输入补偿电压: 工作电源电压:3 V to 5.5 V 电源电流:5 mA 最大功率耗散: 最大工作温度:+ 70 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-20 封装:Reel |

| CS5376-BQ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS5378 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power Single-channel Decimation Filter |

| CS5378_08 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power Single-channel Decimation Filter |

| CS5378-IS | 功能描述:特殊用途放大器 IC LP Single-Ch Decimation Filter RoHS:否 制造商:Texas Instruments 通道数量:Single 共模抑制比(最小值): 输入补偿电压: 工作电源电压:3 V to 5.5 V 电源电流:5 mA 最大功率耗散: 最大工作温度:+ 70 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-20 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。