参数资料

| 型号: | CS5376A-IQZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 9/49页 |

| 文件大小: | 0K |

| 描述: | IC FILTER DGTL MULTI-CH 64-TQFP |

| 标准包装: | 160 |

| 滤波器类型: | 数字 |

| 滤波器数: | 4 |

| 滤波器阶数: | 2nd |

| 电源电压: | 3 V ~ 5 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-TQFP(10x10) |

| 包装: | 管件 |

| 配用: | 598-1778-ND - EVALUATION BOARD FOR CS5376 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页

2008 Fairchild Semiconductor Corporation

www.fairchildsemi.com

FUSB2805 Rev. 1.0.3

17

F

USB2

8

0

5

—

USB2

.0

High

-S

pee

d

OTG

Tra

nsc

e

iv

e

rw

ith

UL

P

I

Inter

fac

e

USB Packet Timing

The USB2.0 specification defines the inter-packet

timing

and

the

UTMI/UTMI+

specifications

define

synchronization and processing delays. The ULPI Rev.

1.1 specification defines the inter-packet delays to

ensure compatibility with USB2.0 and supplemental

specifications.

Pipeline Delays

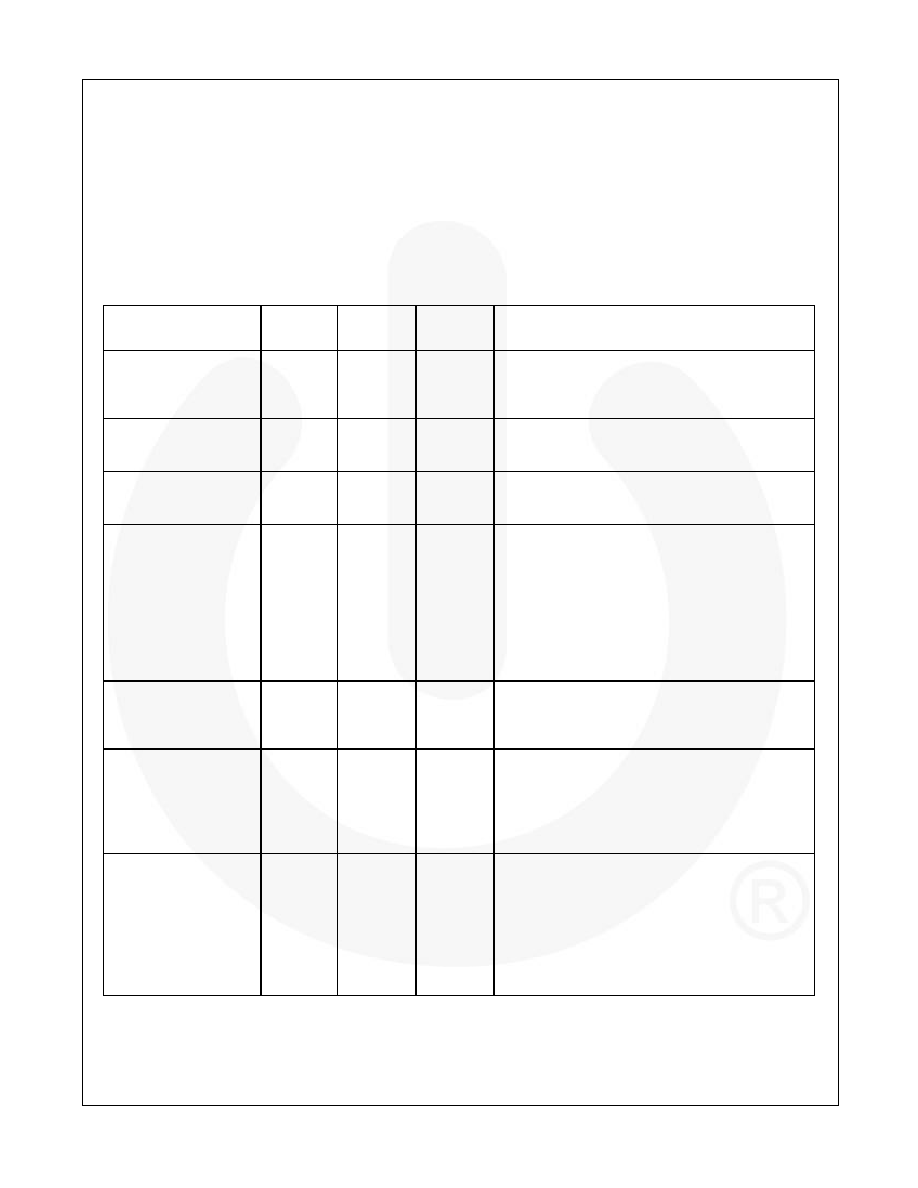

Table 6 describes the delays (in clock cycles) with

which to comply using ULPI. The USB bus events are

measured relative to D+ and D-. The ULPI timings are

relative to the clock edge on which the transition is

detected (i.e. the clock edge on which STP is detected).

Table 6.

Pipeline Delays

Parameter Name

HS PHY

Delay

FS PHY

Delay

LS PHY

Delay

Definition

RXCMD Delay(J/K)

4

Number of clocks after a change in the internal

USB bus state is detected to an RXCMD byte being

sent over the ULPI bus. Applies to all changes

except SE0.

RXCMD Delay(SE0)

4

4 to 6

16 to 18

Number of clocks between the USB bus state

indicating SE0 to an RXCMD byte being sent over

the ULPI bus. Delay is increased due to filtering.

TX Start Delay

1 to 2

6 to 10

74 to 75

Number of clocks between the FUSB2805 detecting

a TXCMD on the ULPI bus to transmitting the first K

of the SYNC pattern on the USB bus.

TX End Delay (packets)

2 to 5

NA

Number of clocks between the FUSB2805 detecting

STP on the ULPI bus to completing EOP

transmission on the USB bus.

HS EOP is completed when all eight consecutive

ones have finished transmitting on the USB bus.

FS/LS packets finish many clock cycles after STP

is asserted. The link must look for RXCMD bytes

indicating SE0-to-J transition to determine when the

transmission is completed on the USB bus.

TX End Delay (SOF)

6 to 9

NA

HS SOF packets have a long EOP. The link must

wait at least nine clocks or for an RXCMD,

indicating squelch (LINESTATE=00b), before

transmitting the next packet.

RX Start Delay

3 to 8

NA

Number of clocks after first K of SYNC pattern is

seen on the USB bus to the simultaneous assertion

of DIR and NXT or an RXCMD indicating RxActive.

Used for HS packets only.

For FS/LS packets, the link must look for RXCMD

bytes indicating J-to-K transition.

RX End Delay

3 to 8

17 to 18

122 to 123

Number of clocks after EOP occurs on the USB bus

to the FUSB2805 de-asserting DIR or indicating

RxActive LOW in an RXCMD byte.

HS EOP is completed when all eight consecutive

ones have finished transmitting on the USB bus.

FS/LS EOP occurs when SE0 starts on the USB

bus. For FS/LS, the link uses LINESTATE and not

RxEnd delay to time USB packets.

Note:

11. Please refer to ULPI Rev 1.1 specifications, section 3.8.2.6.2 for details on PHY pipeline delays.

相关PDF资料 |

PDF描述 |

|---|---|

| CS61577-IL1Z | IC LINE INTERFACE T1/E1 28PLCC |

| CS61584A-IQ3Z | IC LINE INTERFACE T1/E1 64LQFP |

| CS61884-IRZ | IC LN INTERF T1/E1/J1 160-LFBGA |

| CS8130-CS | IC IR TRANSCEIVER 2-5V 20-SSOP |

| CS8190EDWF20G | IC TACH/SPEEDO DRVR PREC 20SOICW |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS5376A-IQZR | 功能描述:特殊用途放大器 LP Multi-Ch. Decimation Filter RoHS:否 制造商:Texas Instruments 通道数量:Single 共模抑制比(最小值): 输入补偿电压: 工作电源电压:3 V to 5.5 V 电源电流:5 mA 最大功率耗散: 最大工作温度:+ 70 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-20 封装:Reel |

| CS5376-BQ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS5378 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power Single-channel Decimation Filter |

| CS5378_08 | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low-power Single-channel Decimation Filter |

| CS5378-IS | 功能描述:特殊用途放大器 IC LP Single-Ch Decimation Filter RoHS:否 制造商:Texas Instruments 通道数量:Single 共模抑制比(最小值): 输入补偿电压: 工作电源电压:3 V to 5.5 V 电源电流:5 mA 最大功率耗散: 最大工作温度:+ 70 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-20 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。