参数资料

| 型号: | CS61884-IRZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 26/72页 |

| 文件大小: | 0K |

| 描述: | IC LN INTERF T1/E1/J1 160-LFBGA |

| 标准包装: | 126 |

| 功能: | 线路接口单元(LIU) |

| 接口: | E1,J1,T1 |

| 电路数: | 8 |

| 电源电压: | 3.14 V ~ 3.47 V |

| 功率(瓦特): | 1.73W |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 160-LFBGA |

| 供应商设备封装: | 160-TFGBA(13x13) |

| 包装: | 散装 |

| 包括: | AMI 编码器和解码器,B8ZS 编码器和解码器,HDB3 编码器和解码器,LOS 检测 |

| 产品目录页面: | 759 (CN2011-ZH PDF) |

| 其它名称: | 598-1717 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

CS61884

32

DS485F3

13. HOST MODE

Host mode allows the CS61884 to be configured

and monitored using an internal register set. (Refer

page 10). The term, “Host mode” applies to both

Parallel Host and Serial Host modes.

All of the internal registers are available in both Se-

rial and Parallel Host mode; the only difference is

in the functions of the interface pins, which are de-

scribed in Table 8.

Serial port operation is compatible with the serial

ports of most microcontrollers. Parallel port opera-

tion can be configured to be compatible with 8-bit

microcontrollers from Motorola or Intel, with both

multiplexed or non-multiplexed address/data bus-

ses. (Refer to Table 9 on page 34 for host mode

registers).

13.1 SOFTWARE RESET

A software reset can be forced by writing the Soft-

page 36). A software reset initializes all registers to

their default settings and initializes all internal state

machines.

13.2 Serial Port Operation

Serial port host mode operation is selected when

the MODE pin is left open or set to VCC/2. In this

mode, the CS61884 register set is accessed by set-

ting the chip select (CS) pin low and communicat-

ing over the SDI, SDO, and SCLK pins. Timing

over the serial port is independent of the transmit

and receive system timing. Figure 13 illustrates the

format of serial port data transfers.

A read or write is initiated by writing an ad-

dress/command byte (ACB) to SDI. Only the

ADR0-ADR4 bits are valid; bits ADR5-ADR6 are

do not cares. During a read cycle, the register data

addressed by the ACB is output on SDO on the next

eight SCLK clock cycles. During a write cycle, the

data byte immediately follows the ACB.

Data is written to and read from the serial port in

LSB first format. When writing to the port, SDI

data is sampled by the device on the rising edge of

SCLK. The valid clock edge of the data on SDO is

controlled by the CLKE pin. When CLKE is low,

data on SDO is valid on the falling edge of SCLK.

When CLKE is high, data on SDO is valid on the

raising edge of SCLK. The SDO pin is Hi-Z when

not transmitting. If the host processor has a bidirec-

tional I/O port, SDI and SDO may be tied together.

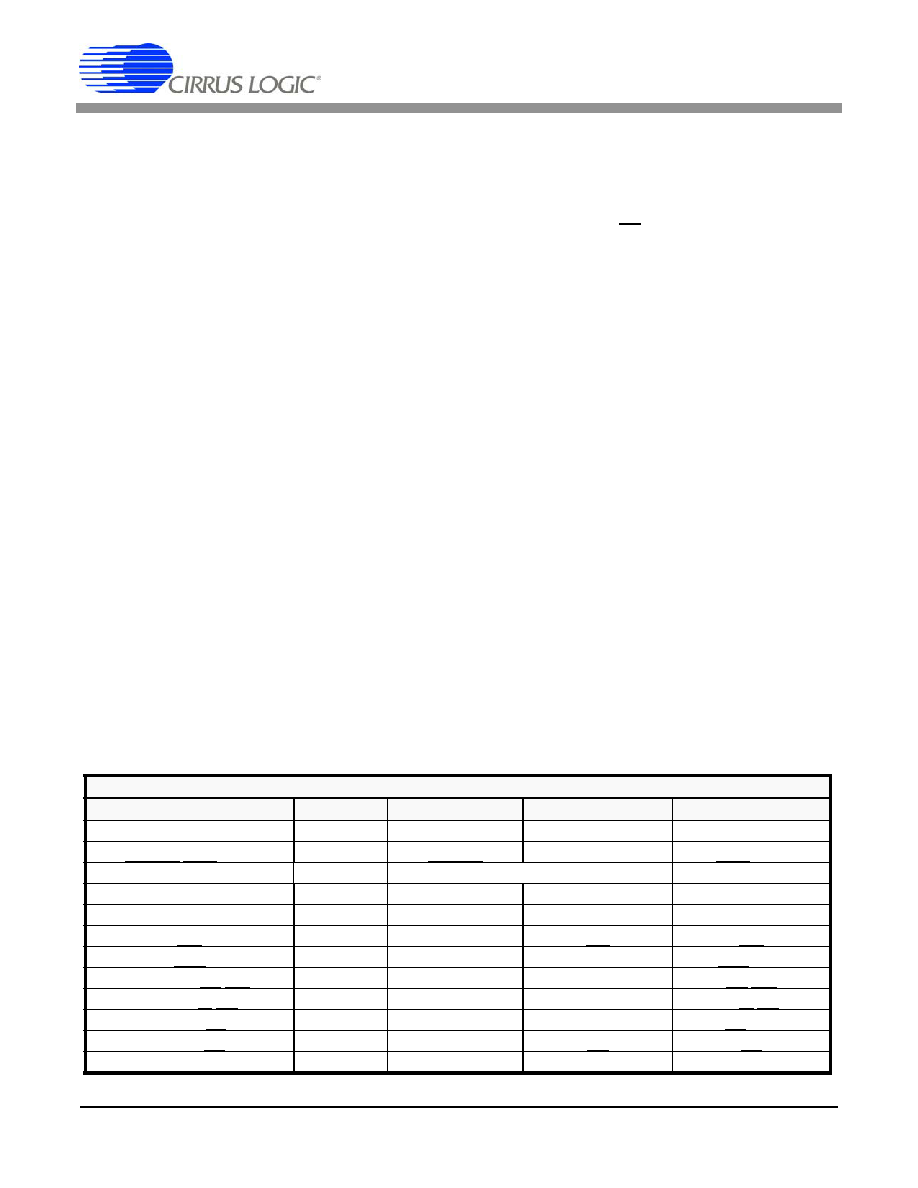

Table 8. Host Control Signal Descriptions

HOST CONTROL SIGNAL DESCRIPTIONS

PIN NAME

PIN #

HARDWARE

SERIAL

PARALLEL

MODE

11

LOW

VDD/2

HIGH

MUX

43

BITSEN0

-

MUX

CODEN/MOT/INTL

88

CODEN

-MOT/INTL

ADDR [4]

12

GND

-

ADDR[4]

ADDR[3:0]

13-16

ADDR[3:0]

-

ADDR [3:0]

LOOP[7:0], DATA[7:0]

28-21

LOOP[7:0]

-

DATA[7:0]

INT

82

Pulled Up

INT

SDO/ACK/RDY

83

NC

SDO

ACK/RDY

LEN0/SDI/DS/WR

84

LEN0

SDI

DS/WR

LEN1/R/W/RD

85

LEN1

-

R/W/RD

LEN2/SCLK/AS/ALE

86

LEN2

SCLK

AS/ALE

JASEL/CS

87

JASEL

CS

相关PDF资料 |

PDF描述 |

|---|---|

| CS8130-CS | IC IR TRANSCEIVER 2-5V 20-SSOP |

| CS8190EDWF20G | IC TACH/SPEEDO DRVR PREC 20SOICW |

| CS8191XNF16 | IC DRVR AIRCORE TACH/SPEED 16DIP |

| CS82C5296 | IC UART/BRG 5V 16MHZ 28-PLCC |

| CS82C59A-1296 | IC CTRL INTERRUPT 12.5MHZ 28PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS61884-IRZR | 功能描述:网络控制器与处理器 IC IC Octal T1/E1/J1 Line Interface Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| CS6193-000 | 功能描述:多芯电缆 RoHS:否 制造商:Alpha Wire 导体数量:3 线规 - 美国线规(AWG):16 绞合:19 x 29 屏蔽:Shielded 长度:100 ft 电压额定值:600 V 外壳材料:Polytetrafluoroethylene (PTFE) 绝缘材料:Polytetrafluoroethylene (PTFE) 类型:Communication and Control |

| CS61N | 功能描述:CM SCREWDRIVER,6IN1,INTERCHANGEA 制造商:apex tool group 系列:* 零件状态:在售 标准包装:1 |

| CS62 | 制造商:Thomas & Betts 功能描述:Cable Accessories Compression Splice Aluminum |

| CS6-20 | 制造商:SUPERWORLD 制造商全称:Superworld Electronics 功能描述:POWER TRANSFORMER |

发布紧急采购,3分钟左右您将得到回复。